Section 13 Direct Memory Access Controller (DMAC)

Rev. 4.00 Sep. 14, 2005 Page 431 of 982

REJ09B0023-0400

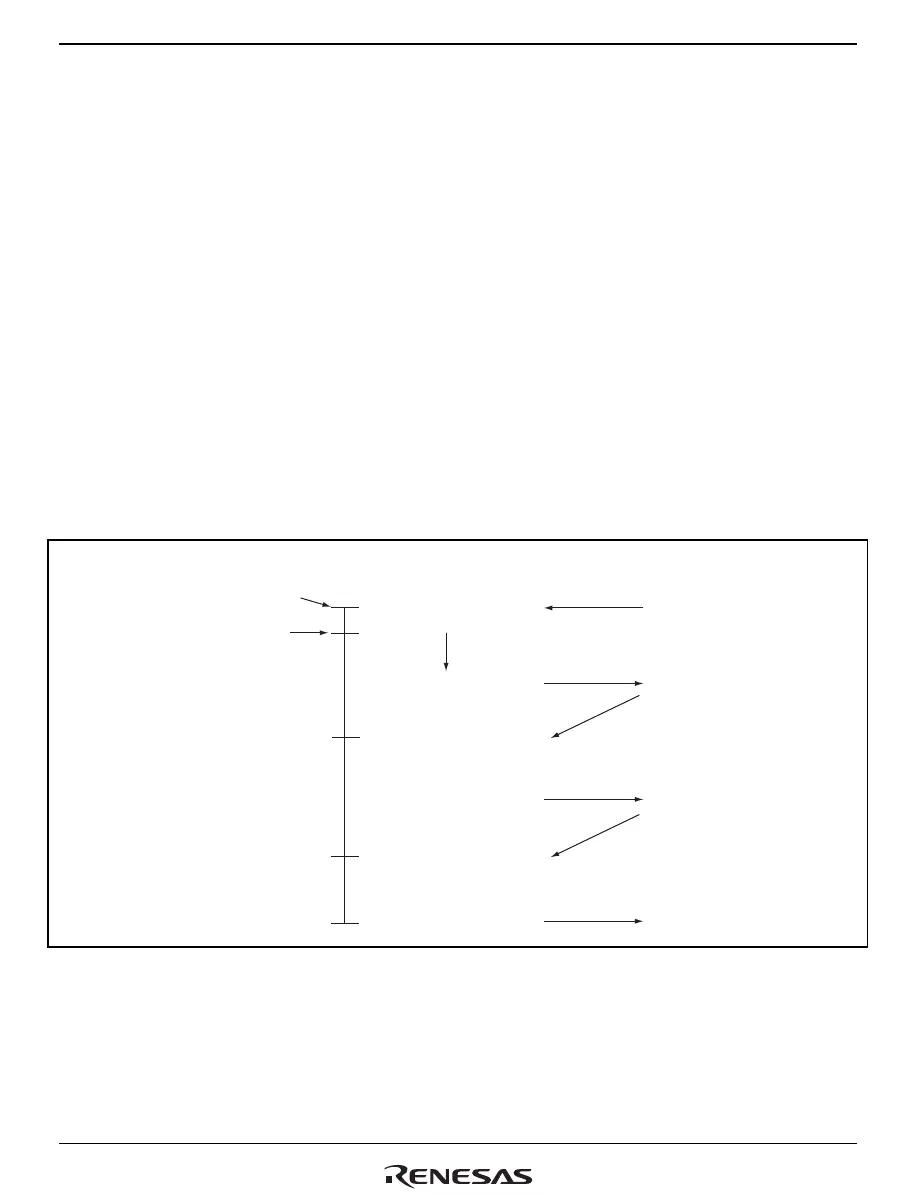

Figure 13.4 shows how the priority order changes when channel 0 and channel 3 transfers are

requested simultaneously and a channel 1 transfer is requested during the channel 0 transfer. The

DMAC operates as follows:

1. Transfer requests are generated simultaneously to channels 0 and 3.

2. Channel 0 has a higher priority, so the channel 0 transfer begins first (channel 3 waits for

transfer).

3. A channel 1 transfer request occurs during the channel 0 transfer (channels 1 and 3 are both

waiting)

4. When the channel 0 transfer ends, channel 0 becomes lowest priority.

5. At this point, channel 1 has a higher priority than channel 3, so the channel 1 transfer begins

(channel 3 waits for transfer).

6. When the channel 1 transfer ends, channel 1 becomes lowest priority.

7. The channel 3 transfer begins.

8. When the channel 3 transfer ends, channels 3 and 2 shift downward in priority so that channel

3 becomes the lowest priority.

Transfer request Waiting channel (s) DMAC operation Channel priority

(1) Channels 0 and 3

(3) Channel 1

0 > 1 > 2 > 3(2) Channel 0 transfer start

(4) Channel 0 transfer ends

(5) Channel 1 transfer starts

(6) Channel 1 transfer ends

(7) Channel 3 transfer starts

(8) Channel 3 transfer ends

1 > 2 > 3 > 0

2 > 3 > 0 > 1

0 > 1 > 2 > 3

Priority order

changes

Priority order

changes

Priority order

changes

None

3

3

1, 3

Figure 13.4 Changes in Channel Priority in Round-Robin Mode

Loading...

Loading...