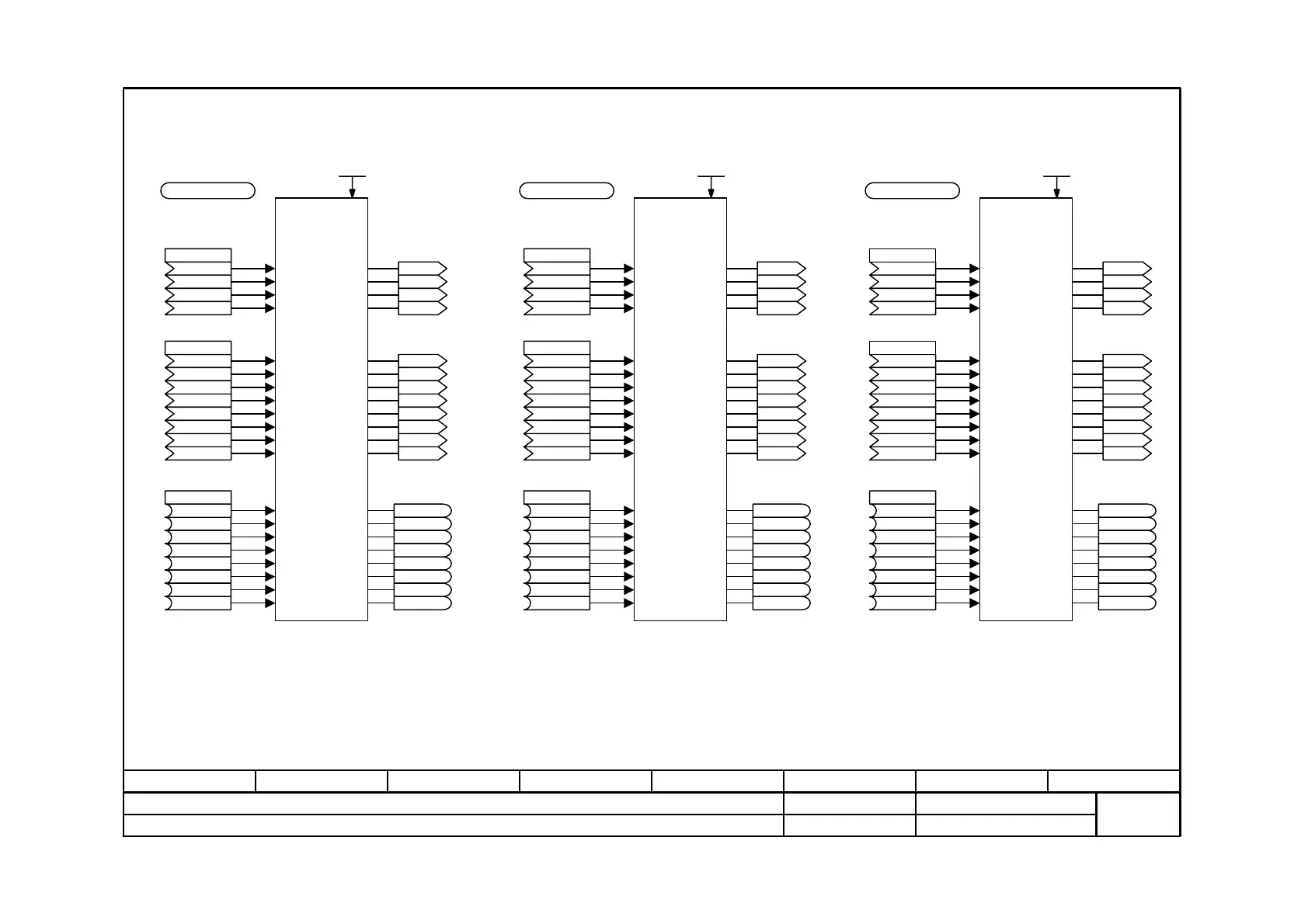

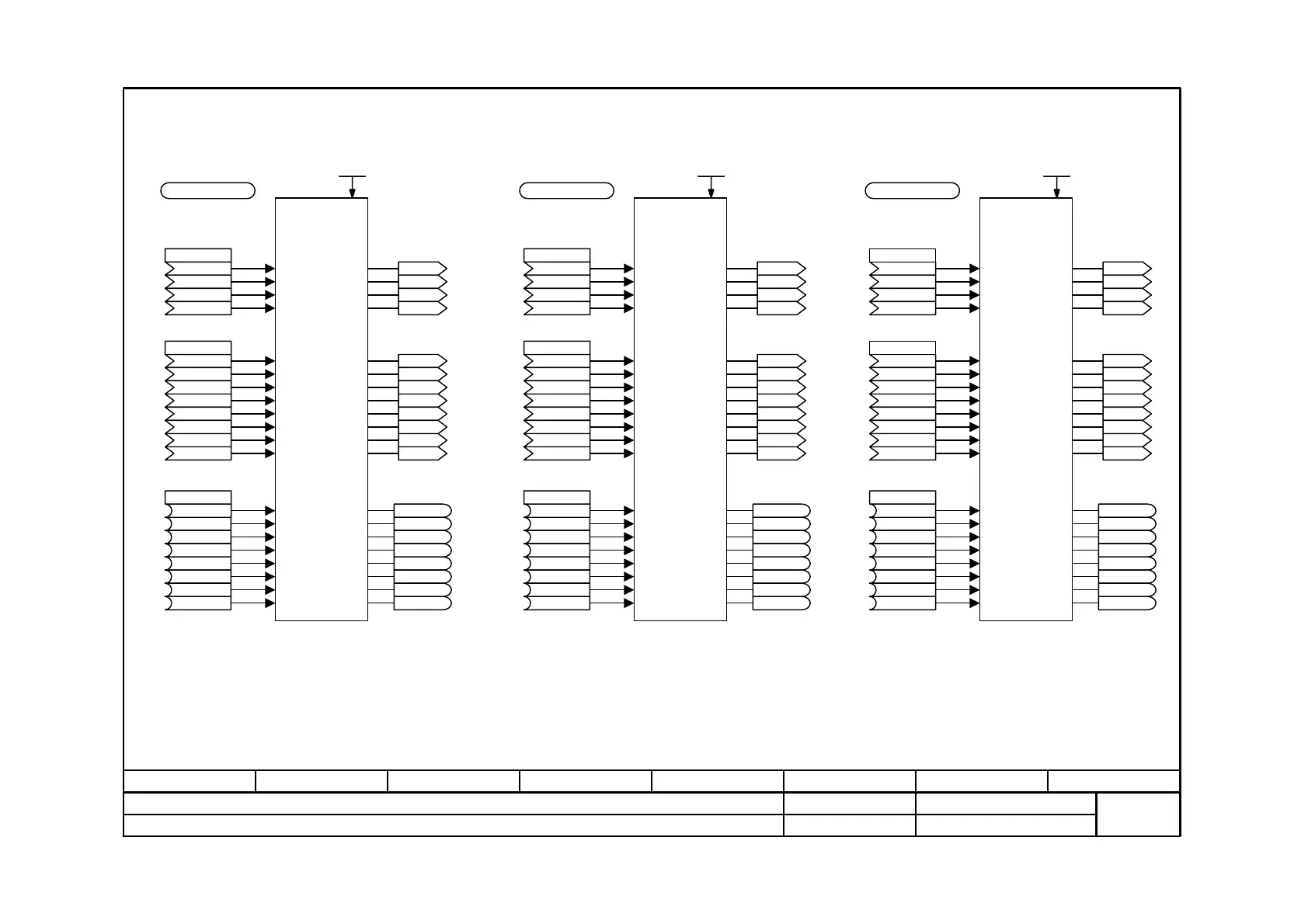

-783 -

Function diagram

87654321

fp_mc_783_e.vsd

Free blocks

MASTERDRIVES MC

08.01.02

Sample & Hold

V2.5

S & H

Tx Ty

Sampling interval

faster time slot

.01

.01

.01

NOTE:

The following settings must be made to ensure consistent coupling of

values from the main processor C167 to the DSP processor:

1. U95x.xx = 2

2. U96x.xx = 0

3. Enter S & H block outputs via P026 into coupling channels

S & H

Tx Ty

Sampling interval

faster time slot

.01

.01

.01

S & H

Tx Ty

Sampling interval

faster time slot

.01

.01

.01

Sampling interval slower time slot

2 ... 10

U060 (2)

U951.68 = ___(20)

KK

U019

Q. SH1 KK

KK

.02

KK

.03

KK

.04

K

U020

Q. SH1 K

K

.02

K

.03

K

.04

K

.05

K

.06

K

.07

K

.08

B

.02

B

.03

B

.04

B

.05

B

.06

B

.07

B

.08

KK0640

KK0641

KK0642

KK0643

K0644

K0645

K0646

K0647

K0648

K0649

K0650

K0651

B0631

B0632

B0633

B0634

B0635

B0636

B0637

B0638

Sampling interval slower time slot

2 ... 10

U349 (2)

U951.70 = ___(20)

KK

U346

Q. SH3 KK

KK

.02

KK

.03

KK

.04

K

U347

Q. SH3 K

K

.02

K

.03

K

.04

K

.05

K

.06

K

.07

K

.08

B

.02

B

.03

B

.04

B

.05

B

.06

B

.07

B

.08

KK0664

KK0665

KK0666

KK0667

K0668

K0669

K0670

K0671

K0672

K0673

K0674

K0675

B0669

B0670

B0671

B0672

B0673

B0674

B0675

B0676

Sampling interval slower time slot

2 ... 10

U270 (2)

U951.69 = ___(20)

KK

U029

Q. SH2 KK

KK

.02

KK

.03

KK

.04

K

U030

Q. SH2 K

K

.02

K

.03

K

.04

K

.05

K

.06

K

.07

K

.08

B

.02

B

.03

B

.04

B

.05

B

.06

B

.07

B

.08

KK0652

KK0653

KK0654

KK0655

K0656

K0657

K0658

K0659

K0660

K0661

K0662

K0663

B0651

B0652

B0653

B0654

B0655

B0656

B0657

B0658

B

U059

Q. SH1 B

B

U348

Q. SH3 B

B

U269

Q. SH2 B

Loading...

Loading...