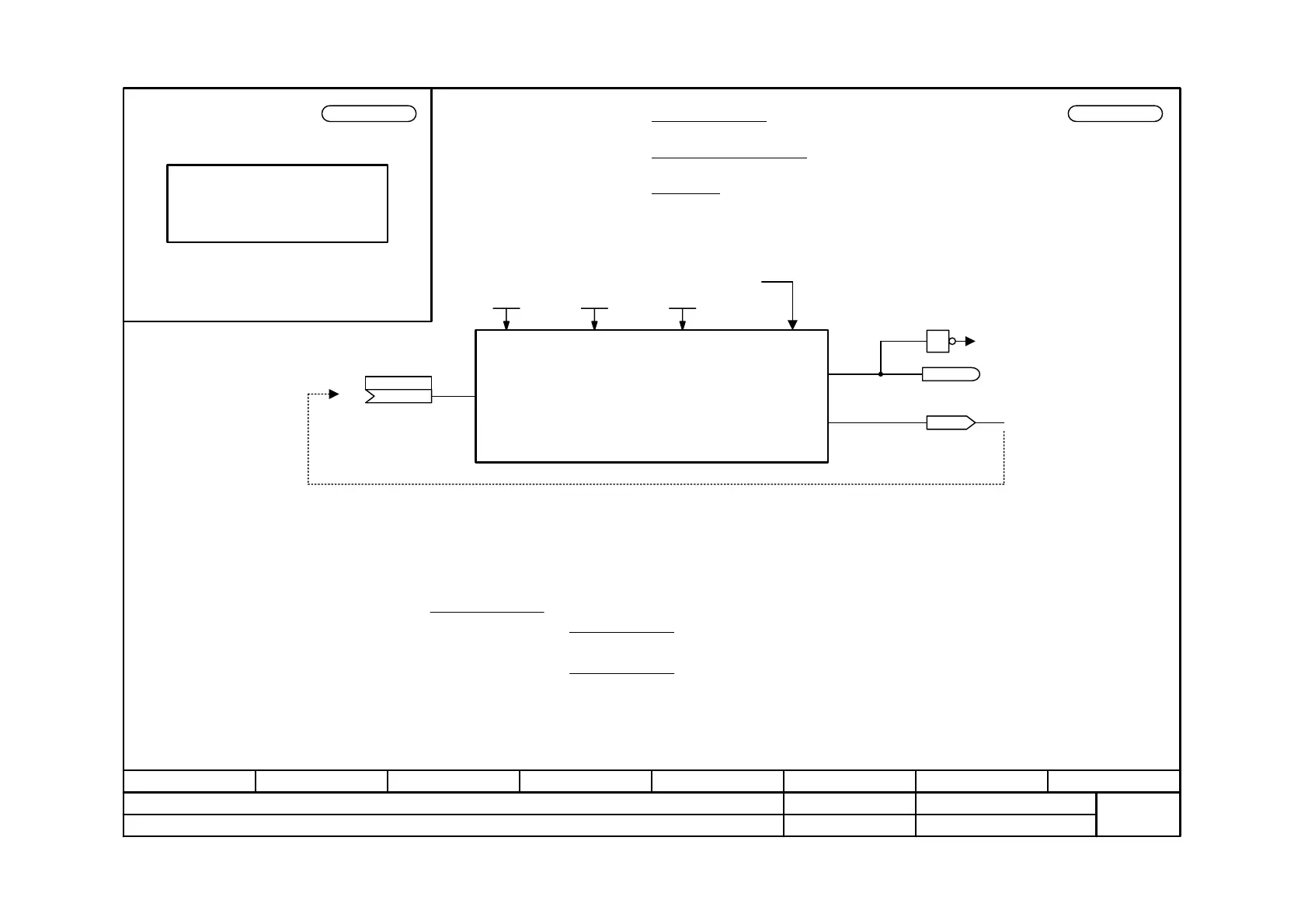

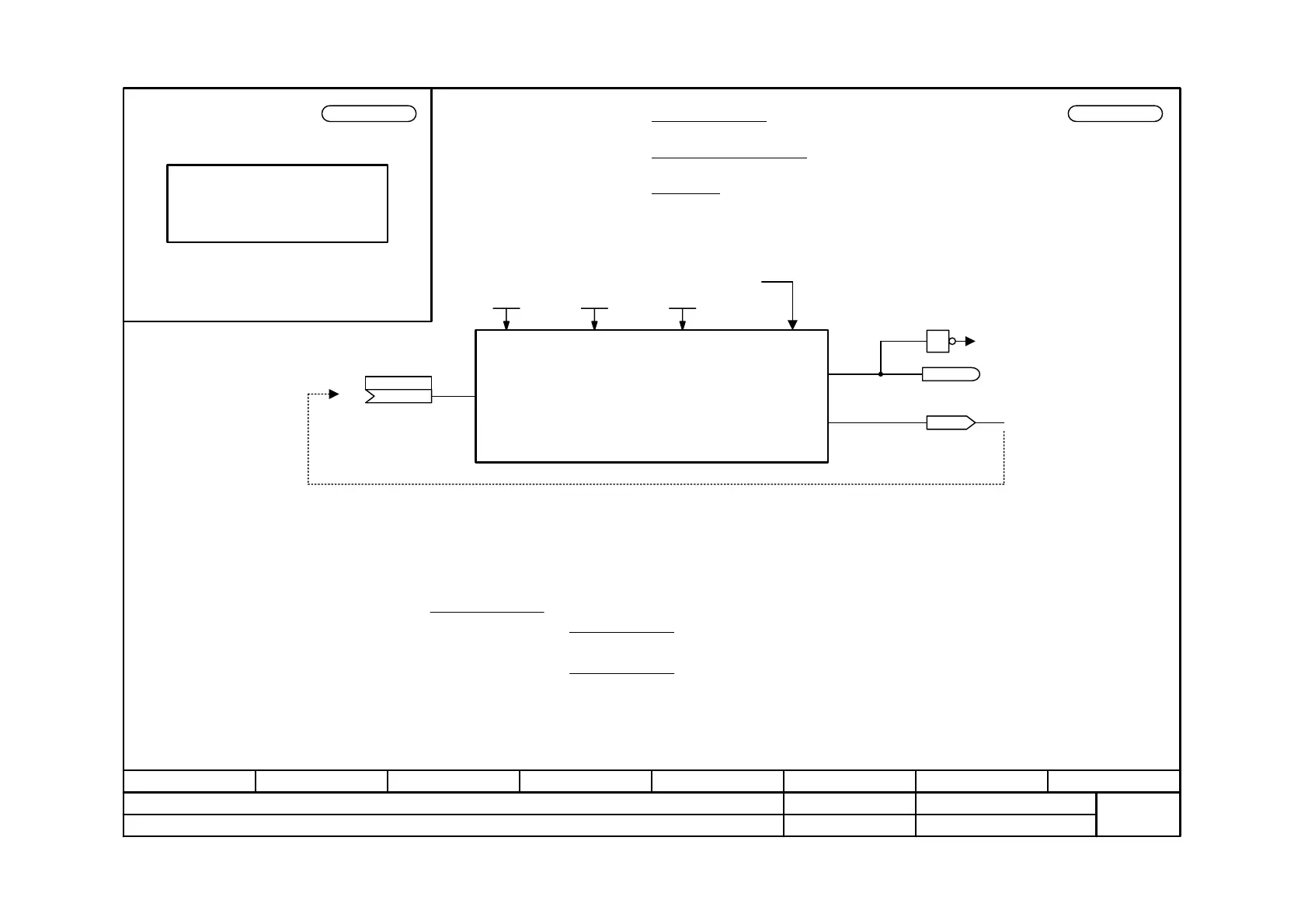

Function diagram

87654321

fp_mc_141_e.vsd

SIMOLINK board (SLB)

MASTERDRIVES MC

23.10.02

Synchronizing

-141 -

V2.5

Synchronizing

PLL

[420.5]

Pulse frequency

1

Alarm A003 "not synchronous"

(with Transceiver)

(Dispatcher only)

Only allowed for PWE 2 or 20 (inactive).

Fine synchronization

SIMOLINK

Setting of P755:

Dead time compensation:

xxx0: No dead time compensation.

xxx1: Compensation of different dead times between units.

SLB switchover (between 2 SLBs):

xx0x: Switchover in operation disabled.

xx1x: Switchover in operation enabled.

Bus cycle time:

x0xx: Bus cycle time is corrected internally over all telegrams.

x1xx: Bus cycle time is exactly implemented.

()

()

()

()

⎟

⎟

⎟

⎠

⎞

⎜

⎜

⎜

⎝

⎛

=

≥

=

⋅=≠

⎟

⎟

⎠

⎞

⎜

⎜

⎝

⎛

≥

=

⋅==

slottime edsynchroniz largest754P

2m

slot time edsynchroniz smallestm

2

340P frequencyPulse

1

746P timeCycle :0754P

2n

slottime edsynchroniz largestn

2

340P frequencyPulse

1

746P timeCycle :0754P

:conditionsingSynchroniz

m

n

Fine synchronization can cause a smaller

synchronization deviation (r748.9).

Fine synchronization has a greater effect the

higher the bus cycle time (P746)/T2 ratio.

n959.22 = 4

Maximum

synchronized

time slot

0...10

P754 (0)

K

P753 (0)

Sync time counter

[140.1]

SIMOLINK

cycle time

B0043 Drive in synchronism

K0260

Time counter

SIMOLINK

configuration

0000 ... 1111

P755 (0)

U950.22 = ___(20)

Loading...

Loading...