6.5.4 Interrupt Enable Register (IER) and Debug Interrupt Enable Register (DBGIER)

PIE Interrupt Registers

www.ti.com

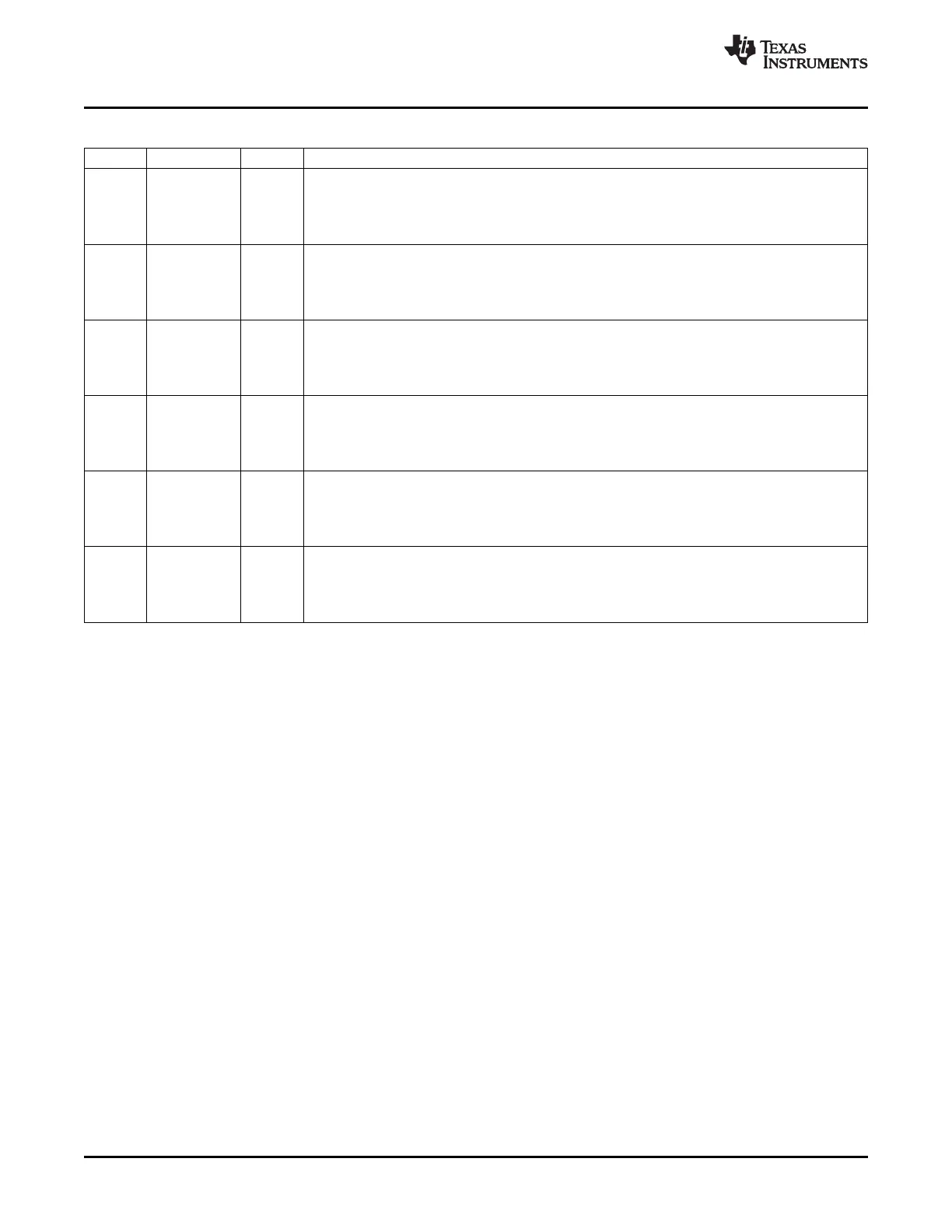

Table 6-11. Interrupt Flag Register (IFR) — CPU Register Field Descriptions (continued)

Bits Field Value Description

5 INT6 Interrupt 6 flag. INT6 is the flag for interrupts connected to CPU interrupt level INT6.

0 No INT6 interrupt is pending

1 At least one INT6 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

4 INT5 Interrupt 5 flag. INT5 is the flag for interrupts connected to CPU interrupt level INT5.

0 No INT5 interrupt is pending

1 At least one INT5 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

3 INT4 Interrupt 4 flag. INT4 is the flag for interrupts connected to CPU interrupt level INT4.

0 No INT4 interrupt is pending

1 At least one INT4 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

2 INT3 Interrupt 3 flag. INT3 is the flag for interrupts connected to CPU interrupt level INT3.

0 No INT3 interrupt is pending

1 At least one INT3 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

1 INT2 Interrupt 2 flag. INT2 is the flag for interrupts connected to CPU interrupt level INT2.

0 No INT2 interrupt is pending

1 At least one INT2 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

0 INT1 Interrupt 1 flag. INT1 is the flag for interrupts connected to CPU interrupt level INT1.

0 No INT1 interrupt is pending

1 At least one INT1 interrupt is pending. Write a 0 to this bit to clear it to 0 and clear the interrupt

request

The IER is a 16-bit CPU register. The IER contains enable bits for all the maskable CPU interrupt levels

(INT1-INT14, RTOSINT and DLOGINT). Neither NMI nor XRS is included in the IER; thus, IER has no

effect on these interrupts.

You can read the IER to identify enabled or disabled interrupt levels, and you can write to the IER to

enable or disable interrupt levels. To enable an interrupt level, set its corresponding IER bit to one using

the OR IER instruction. To disable an interrupt level, set its corresponding IER bit to zero using the AND

IER instruction. When an interrupt is disabled, it is not acknowledged, regardless of the value of the INTM

bit. When an interrupt is enabled, it is acknowledged if the corresponding IFR bit is one and the INTM bit

is zero.

When using the OR IER and AND IER instructions to modify IER bits make sure they do not modify the

state of bit 15 (RTOSINT) unless a real-time operating system is present.

When a hardware interrupt is serviced or an INTR instruction is executed, the corresponding IER bit is

cleared automatically. When an interrupt is requested by the TRAP instruction the IER bit is not cleared

automatically. In the case of the TRAP instruction if the bit needs to be cleared it must be done by the

interrupt service routine.

At reset, all the IER bits are cleared to 0, disabling all maskable CPU level interrupts.

The IER register is shown in Figure 6-12 , and descriptions of the bits follow the figure.

Peripheral Interrupt Expansion (PIE)144 SPRUFB0C – September 2007 – Revised May 2009

Submit Documentation Feedback

Loading...

Loading...