Clocking and System Control

www.ti.com

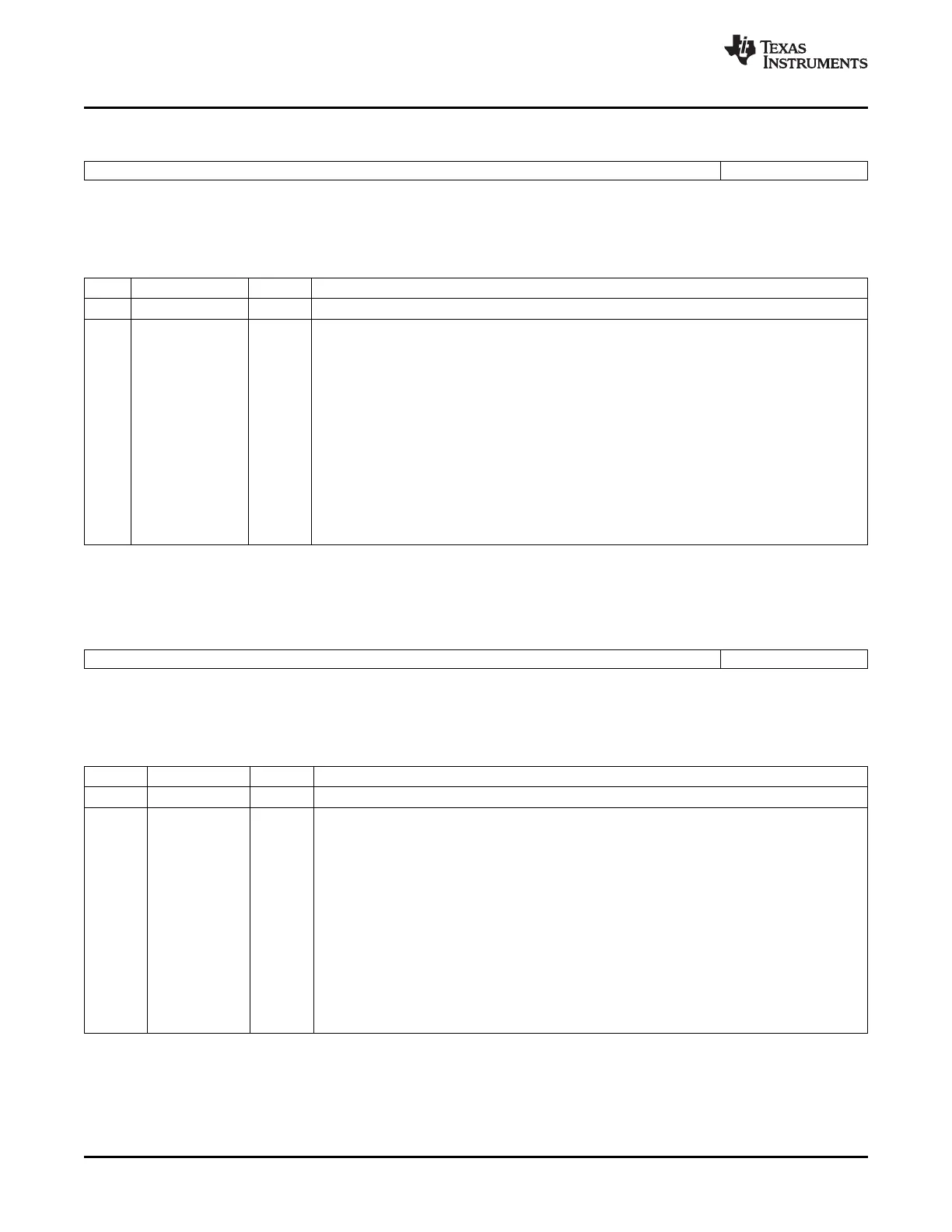

Figure 3-5. High-Speed Peripheral Clock Prescaler (HISPCP) Register

15 3 2 0

Reserved HSPCLK

R-0 R/W-001

LEGEND: R/W = Read/Write; R = Read only; - n = value after reset

Table 3-5. High-Speed Peripheral Clock Prescaler (HISPCP) Field Descriptions

Bits Field Value Description

(1)

15-3 Reserved Reserved

2-0 HSPCLK These bits configure the high-speed peripheral clock (HSPCLK) rate relative to SYSCLKOUT:

If HISPCP

(2)

≠ 0, HSPCLK = SYSCLKOUT/(HISPCP X 2)

If HISPCP = 0, HSPCLK = SYSCLKOUT

000 High speed clock = SYSCLKOUT/1

001 High speed clock = SYSCLKOUT/2 (reset default)

010 High speed clock = SYSCLKOUT/4

011 High speed clock = SYSCLKOUT/6

100 High speed clock = SYSCLKOUT/8

101 High speed clock = SYSCLKOUT/10

110 High speed clock = SYSCLKOUT/12

111 High speed clock = SYSCLKOUT/14

(1)

This register is EALLOW protected. See Section 5.2 for more information.

(2)

HISPCP in this equation denotes the value of bits 2:0 in the HISPCP register.

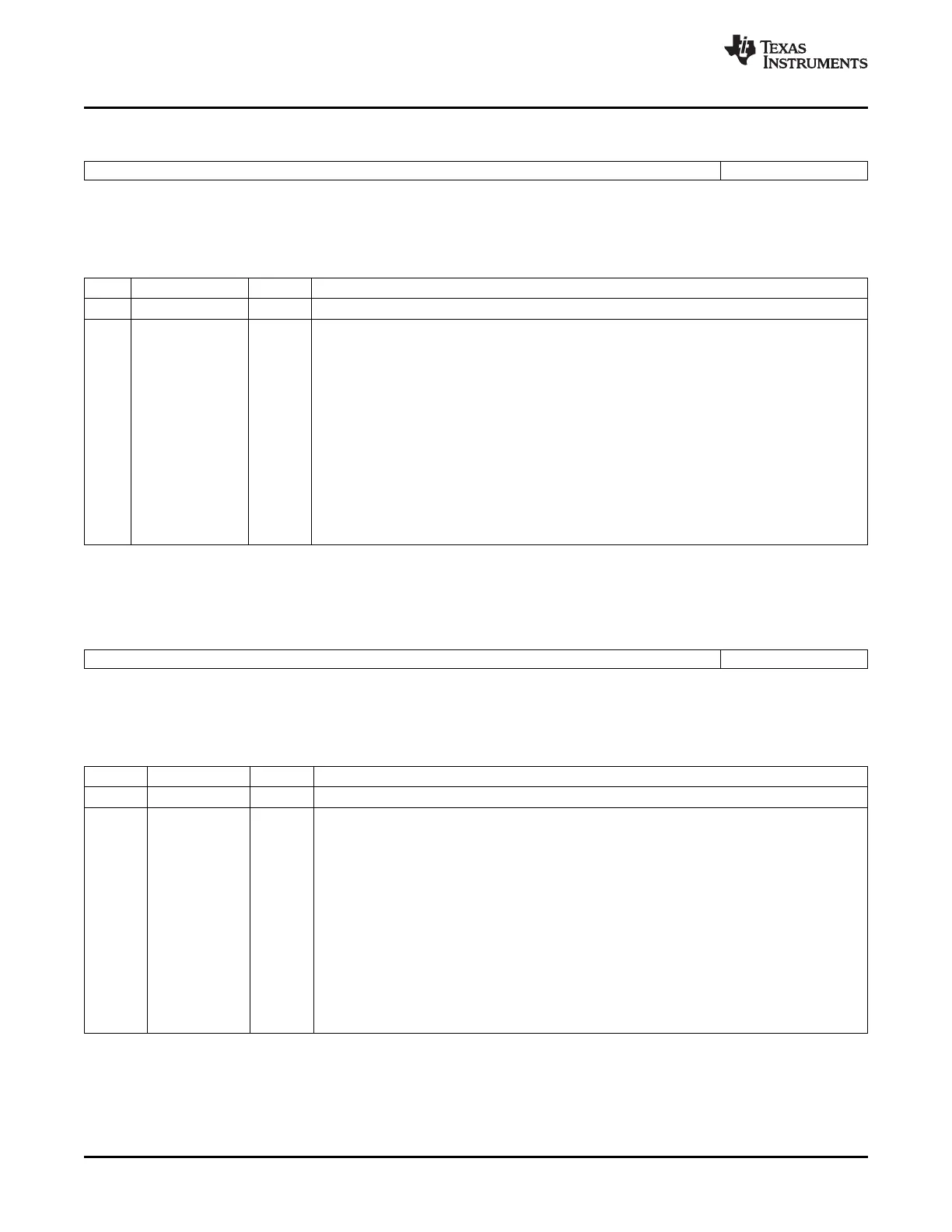

Figure 3-6. Low-Speed Peripheral Clock Prescaler Register (LOSPCP)

15 3 2 0

Reserved LSPCLK

R-0 R/W-010

LEGEND: R/W = Read/Write; R = Read only; - n = value after reset

Table 3-6. Low-Speed Peripheral Clock Prescaler Register (LOSPCP) Field Descriptions

Bits Field Value Description

(1)

15-3 Reserved Reserved

2-0 LSPCLK These bits configure the low-speed peripheral clock (LSPCLK) rate relative to SYSCLKOUT:

If LOSPCP

(2)

≠ 0, then LSPCLK = SYSCLKOUT/(LOSPCP X 2)

If LOSPCP = 0, then LSPCLK = SYSCLKOUT

000 Low speed clock = SYSCLKOUT/1

001 Low speed clock= SYSCLKOUT/2

010 Low speed clock= SYSCLKOUT/4 (reset default)

011 Low speed clock= SYSCLKOUT/6

100 Low speed clock= SYSCLKOUT/8

101 Low speed clock= SYSCLKOUT/10

110 Low speed clock= SYSCLKOUT/12

111 Low speed clock= SYSCLKOUT/14

(1)

This register is EALLOW protected. See Section 5.2 for more information.

(2)

LOSPCP in this equation denotes the value of bits 2:0 in the LOSPCP register.

Clocking44 SPRUFB0C – September 2007 – Revised May 2009

Submit Documentation Feedback

Loading...

Loading...