Low-Power Modes Block

www.ti.com

Table 3-11. Low Power Modes (continued)

Mode Description

HALT If the LPM bits in the LPMCR0 register are set to 1x, the device enters the HALT mode when the IDLE

Mode: instruction is executed. In HALT mode all of the device clocks, including the PLL and oscillator, are shut down.

Before entering the HALT mode, you should perform the following tasks:

• Enable the WAKEINT interrupt in the PIE module (PIEIER1.8 = 1). This interrupt is connected to both the

watchdog and the Low-Power-Mode module interrupt.

• Specify one of the GPIO port A signals to wake the device in the GPIOLPMSEL register. The

GPIOLPMSEL register is part of the GPIO module. In addition to the selected GPIO signal, the XRS input

can also wake the device from the HALT mode

• Disable all interrupts with the possible exception of the HALT mode wakeup interrupt. The interrupts can be

re-enabled after the device is brought out of HALT mode.

• For device to exit HALT mode properly, the following conditions must be met:

Bit 7 (INT1.8) of PIEIER1 register should be 1.

Bit 0 (INT1) of IER register must be 1.

• If the above conditions are met,

– WAKE_INT ISR will be executed first, followed by the instruction(s) after IDLE, if INTM = 0.

– WAKE_INT ISR will not be executed and instruction(s) after IDLE will be executed, if INTM = 1.

Do not enter HALT low power mode when the device is operating in limp mode (PLLSTS[MCLKSTS] = 1).

If you try to enter HALT mode when the device is already operating in limp mode then the device may not

properly enter HALT. The device may instead enter STANDBY mode or may hang and you may not be able to

exit HALT mode. For this reason, always check that the PLLSTS[MCLKSTS] bit = 0 before entering HALT mode.

When the selected external signal goes low, it is fed asynchronously to the LPM block. The oscillator is turned

on and begins to power up. You must hold the signal low long enough for the oscillator to complete power up.

Once the oscillator has stabilized, the PLL lock sequence is initiated. Once the PLL has locked, it feeds the

CLKIN to the CPU at which time the CPU responds to the WAKEINT interrupt if enabled.

The low-power modes are controlled by the LPMCR0 register (Figure 3-13 ).

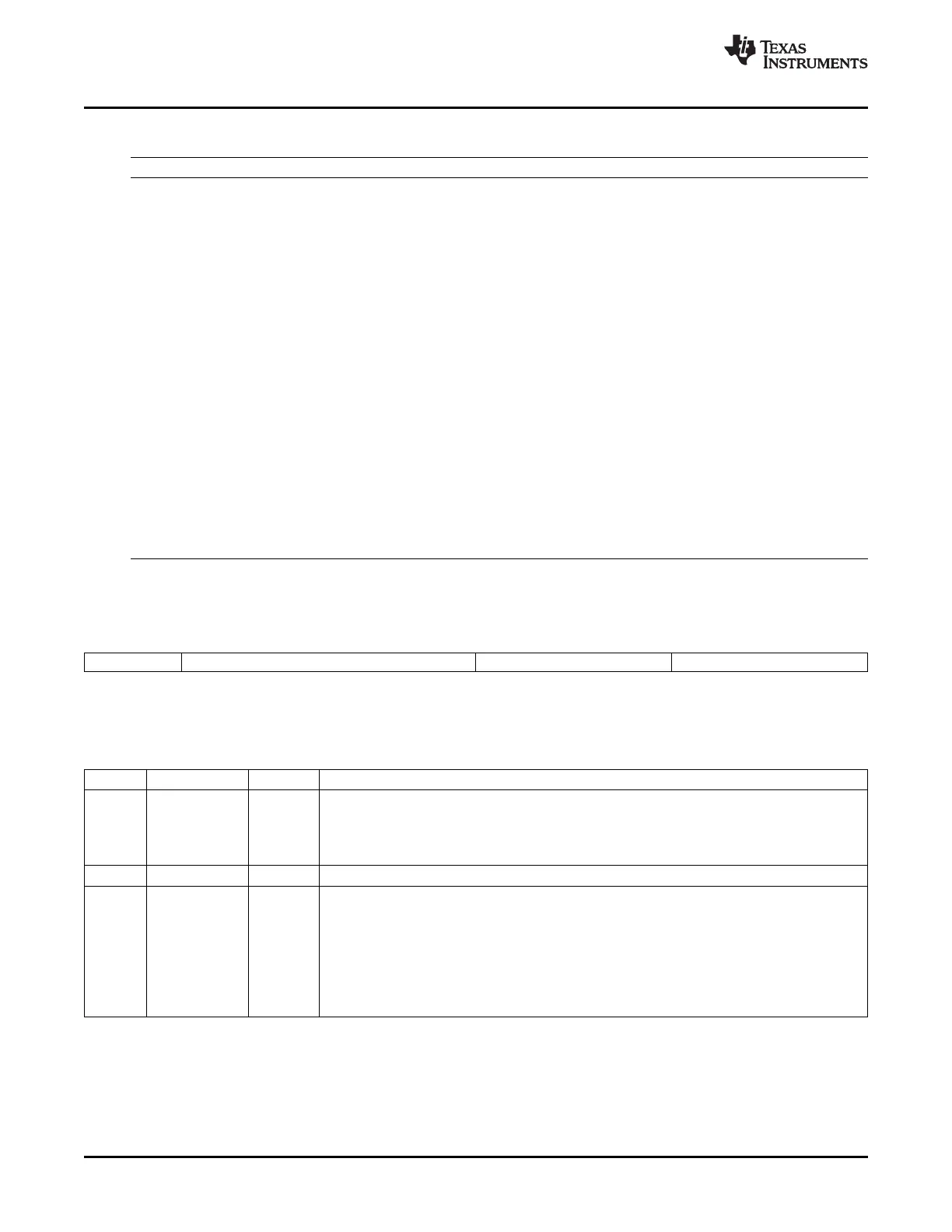

Figure 3-13. Low Power Mode Control 0 Register (LPMCR0)

15 14 8 7 2 1 0

WDINTE Reserved QUALSTDBY LPM

R/W-0 R-0 R/W-1 R/W-0

LEGEND: R/W = Read/Write; R = Read only; - n = value after reset

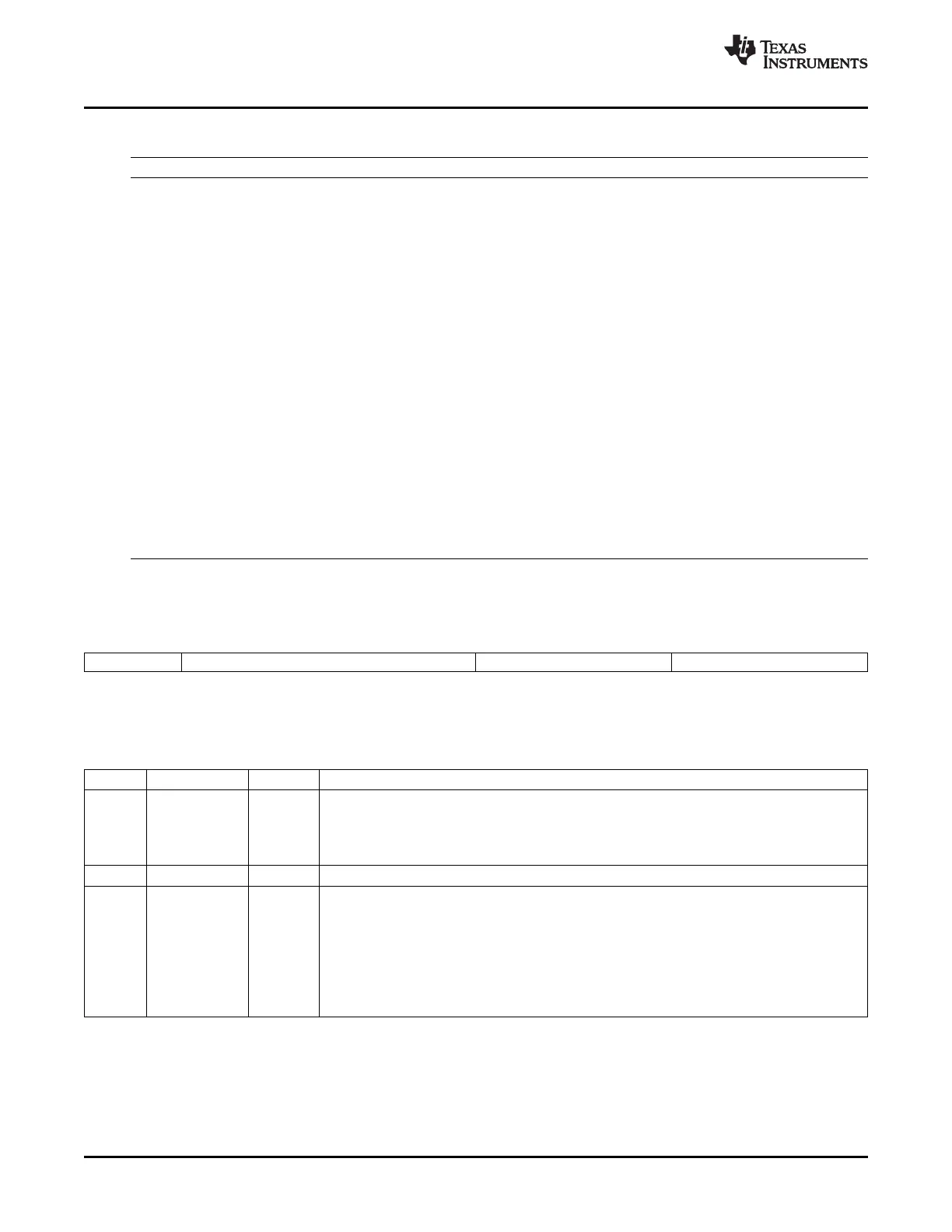

Table 3-12. Low Power Mode Control 0 Register (LPMCR0) Field Descriptions

Bits Field Value Description

(1)

15 WDINTE Watchdog interrupt enable

0 The watchdog interrupt is not allowed to wake the device from STANDBY. (default)

The watchdog is allowed to wake the device from STANDBY. The watchdog interrupt must also

1

be enabled in the SCSR Register.

14-8 Reserved Reserved

7-2 QUALSTDBY Select number of OSCCLK clock cycles to qualify the selected GPIO inputs that wake the device

from STANDBY mode. This qualification is only used when in STANDBY mode. The GPIO

signals that can wake the device from STANDBY are specified in the GPIOLPMSEL register.

000000 2 OSCCLKs (default)

000001 3 OSCCLKs

. . . . . .

111111 65 OSCCLKs

(1)

This register is EALLOW protected. See Section 5.2 for more information.

Clocking54 SPRUFB0C – September 2007 – Revised May 2009

Submit Documentation Feedback

Loading...

Loading...