www.ti.com

External Interrupt Control Registers

Table 6-15. External NMI Interrupt Control Register (XNMICR) Field Descriptions (continued)

Bits Field Value Description

1 Select Select the source for INT13

0 Timer 1 connected To INT13

1 XNMI_XINT13 connected To INT13

0 Enable This read/write bit enables or disables external interrupt NMI

0 Disable XNMI interrupt

1 Enable XNMI interrupt

The XNMI Control Register (XNMICR) can be used to enable or disable the NMI interrupt to the CPU. In

addition, you can select the source for the INT13 CPU interrupt. The source of the INT13 interrupt can be

either the internal CPU Timer1 or the external GPIO signal assigned to XNMI.

The INT13 interrupt can be connected to XNMI_XINT13 for customer use.

Table 6-16 shows the relationship between the XNMICR Register settings and the interrupt sources to the

28x CPU.

Table 6-16. XNMICR Register Settings and Interrupt Sources

XNMICR Register Bits 28x CPU Interrupt Timestamp

ENABLE SELECT NMI Source INT13 Source (XNMICTR)

0 0 Disabled CPU Timer 1 None

0 1 Disabled XNMI None

1 0 XNMI CPU Timer 1 XNMI

1 1 Disabled XNMI XNMI

For XINT1 and XINT2, there is also a 16-bit counter that is reset to 0x000 whenever an interrupt edge is

detected. These counters can be used to accurately time stamp an occurrence of the interrupt.

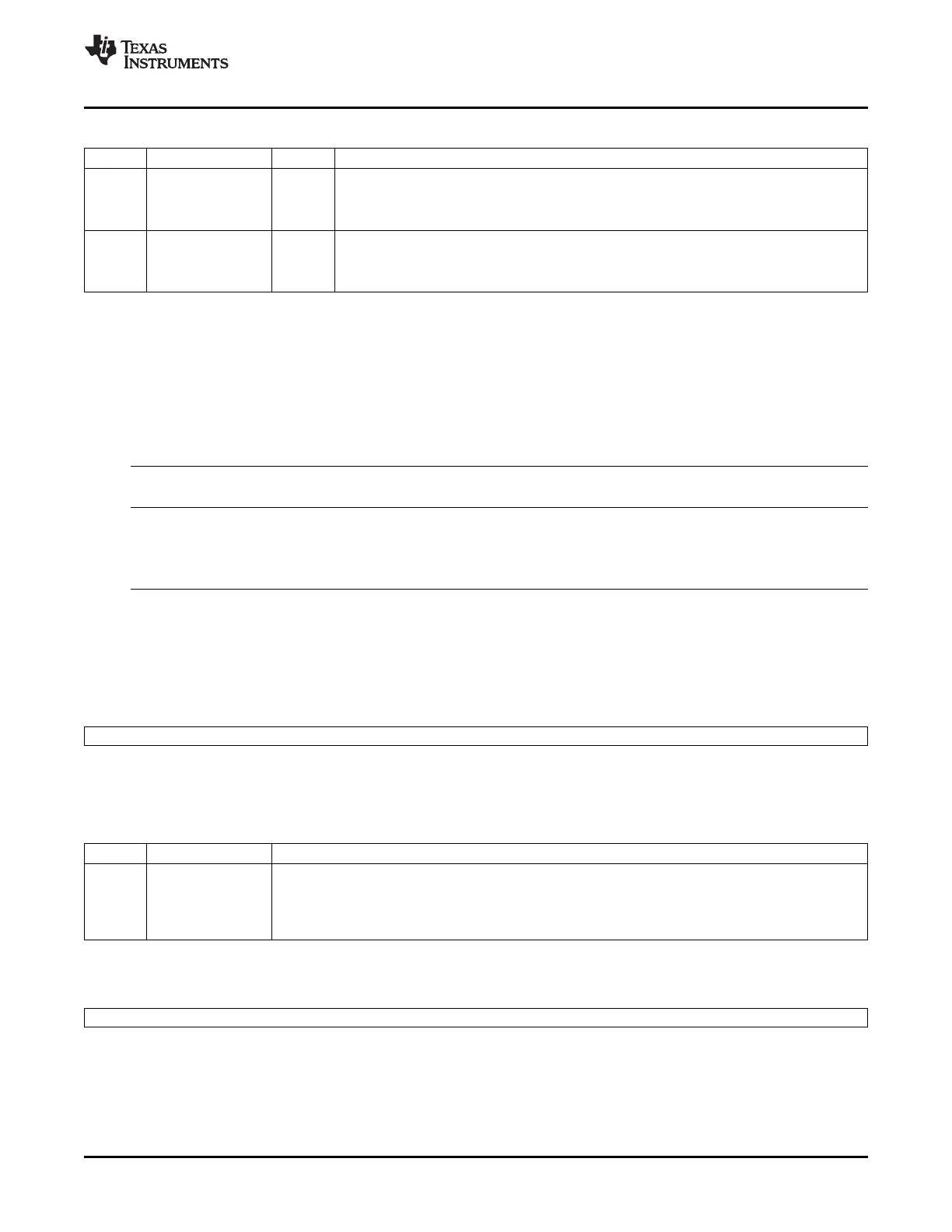

Figure 6-16. External Interrupt 1 Counter (XINT1CTR) (Address 7078h)

15 0

INTCTR[15-0]

R-0

LEGEND: R/W = Read/Write; R = Read only; - n = value after reset

Table 6-17. External Interrupt 1 Counter (XINT1CTR) Field Descriptions

Bits Field Description

15-0 INTCTR This is a free running 16-bit up-counter that is clocked at the SYSCLKOUT rate. The counter value is

reset to 0x0000 when a valid interrupt edge is detected and then continues counting until the next valid

interrupt edge is detected. When the interrupt is disabled, the counter stops. The counter is a free-running

counter and wraps around to zero when the max value is reached. The counter is a read only register and

can only be reset to zero by a valid interrupt edge or by reset.

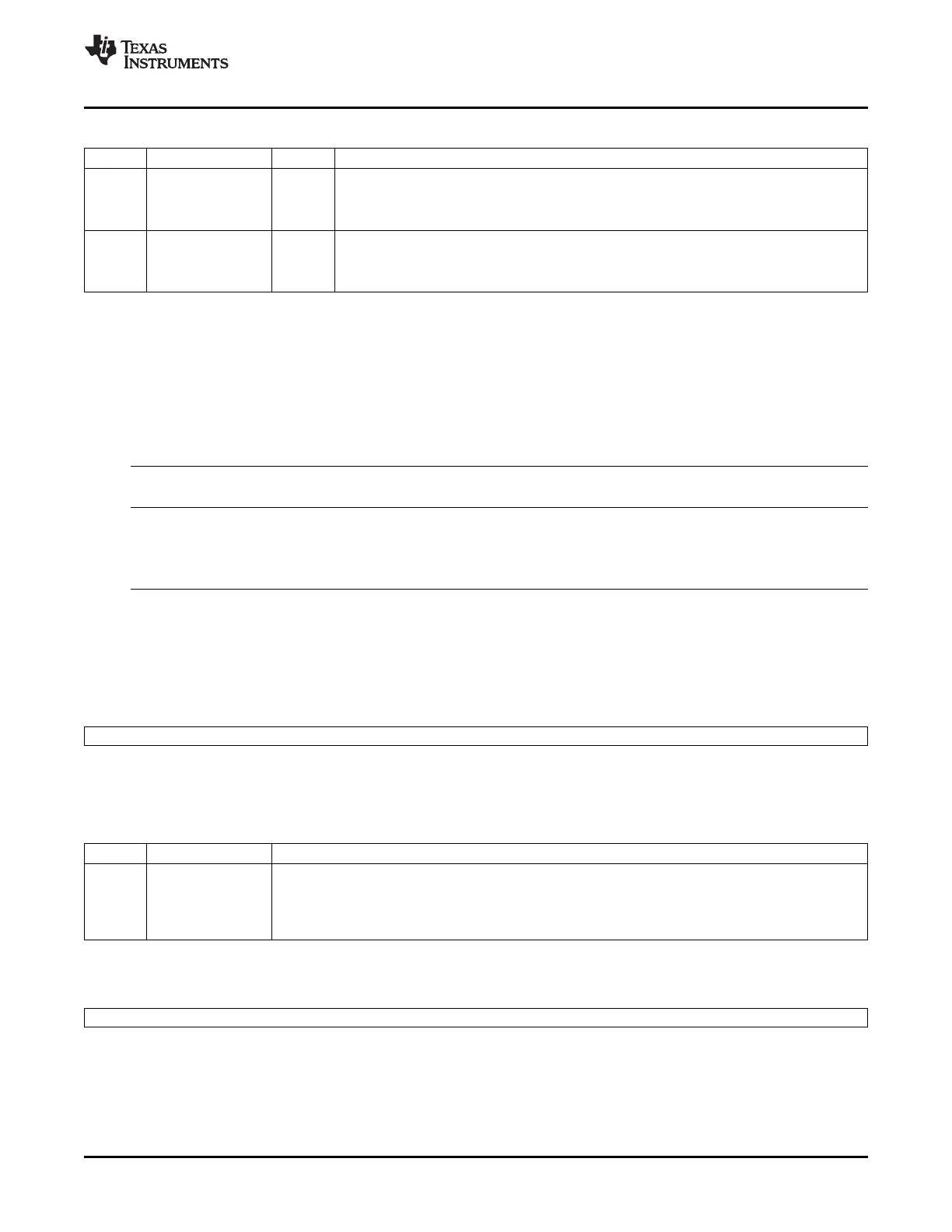

Figure 6-17. External Interrupt 2 Counter (XINT2CTR) (Address 7079h)

15 0

INTCTR[15-0]

R-0

LEGEND: R/W = Read/Write; R = Read only; - n = value after reset

SPRUFB0C – September 2007 – Revised May 2009 Peripheral Interrupt Expansion (PIE) 149

Submit Documentation Feedback

Loading...

Loading...