www.ti.com

Clocking and System Control

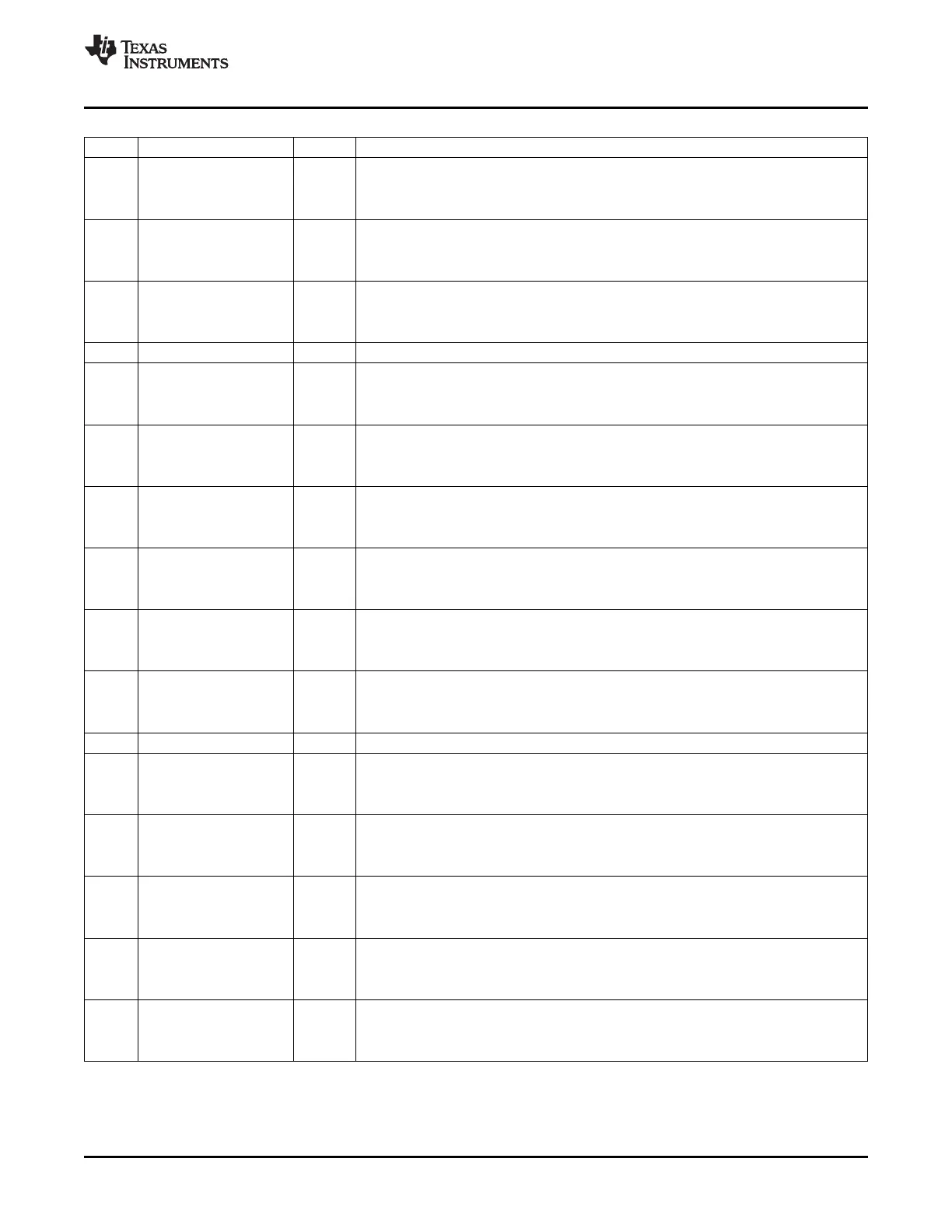

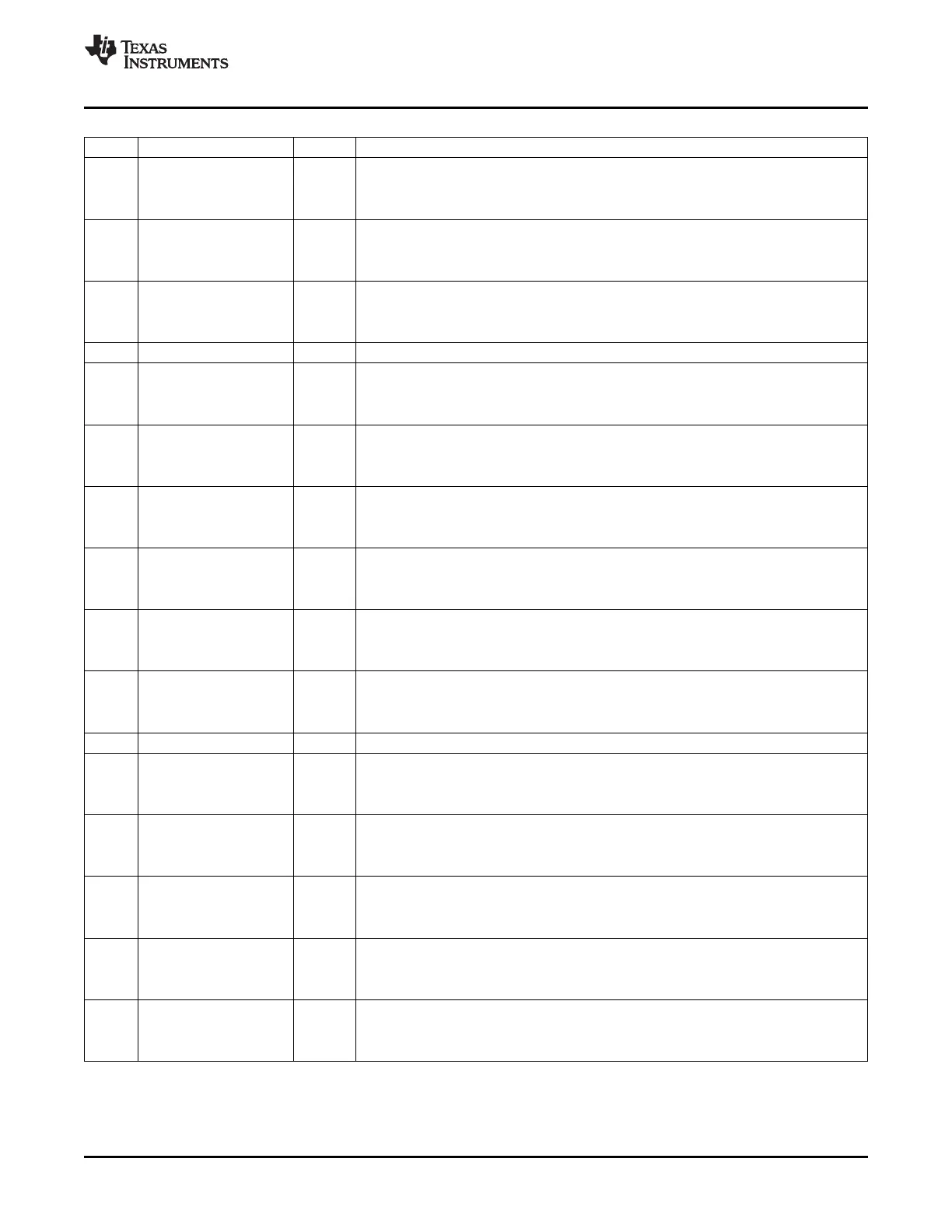

Table 3-3. Peripheral Clock Control 1 Register (PCLKCR1) Field Descriptions

Bits Field Value Description

(1)

15 EQEP2ENCLK eQEP2 clock enable

0 The eQEP2 module is not clocked. (default)

(2)

1 The eQEP2 module is clocked by the system clock (SYSCLKOUT).

14 EQEP1ENCLK eQEP1 clock enable

0 The eQEP1 module is not clocked. (default)

(2)

1 The eQEP1 module is clocked by the system clock (SYSCLKOUT).

14 EQEP1ENCLK eQEP1 clock enable

0 The eQEP1 module is not clocked. (default)

(2)

1 The eQEP1 module is clocked by the system clock (SYSCLKOUT).

13-9 Reserved

13 ECAP6ENCLK eCAP6 clock enable. This bit is reserved on devices without the eCAP6 module.

0 The eCAP6 module is not clocked. (default)

1 The eCAP6 module is clocked by the system clock (SYSCLKOUT).

12 ECAP5ENCLK eCAP5 clock enable. This bit is reserved on devices without the eCAP5 module.

0 The eCAP5 module is not clocked. (default)

1 The eCAP5 module is clocked by the system clock (SYSCLKOUT).

11 ECAP4ENCLK eCAP4 clock enable

0 The eCAP4 module is not clocked. (default)

(2)

1 The eCAP4 module is clocked by the system clock (SYSCLKOUT).

10 ECAP3ENCLK eCAP3 clock enable

0 The eCAP3 module is not clocked. (default)

(2)

1 The eCAP3 module is clocked by the system clock (SYSCLKOUT).

9 ECAP2ENCLK eCAP2 clock enable

0 The eCAP2 module is not clocked. (default)

(2)

1 The eCAP2 module is clocked by the system clock (SYSCLKOUT).

8 ECAP1ENCLK eCAP1 clock enable

0 The eCAP1 module is not clocked. (default)

(2)

1 The eCAP1 module is clocked by the system clock (SYSCLKOUT).

7:6 Reserved 0 Reserved

5 EPWM6ENCLK ePWM6 clock enable

(3)

0 The ePWM6 module is not clocked. (default)

(2)

1 The ePWM6 module is clocked by the system clock (SYSCLKOUT).

4 EPWM5ENCLK ePWM5 clock enable

(3)

0 The ePWM5 module is not clocked. (default)

(2)

1 The ePWM5 module is clocked by the system clock (SYSCLKOUT).

3 EPWM4ENCLK ePWM4 clock enable.

(3)

0 The ePWM4 module is not clocked. (default)

(2)

1 The ePWM4 module is clocked by the system clock (SYSCLKOUT).

2 EPWM3ENCLK ePWM3 clock enable.

(3)

0 The ePWM3 module is not clocked. (default)

(2)

1 The ePWM3 module is clocked by the system clock (SYSCLKOUT).

1 EPWM2ENCLK ePWM2 clock enable.

(3)

0 The ePWM2 module is not clocked. (default)

(2)

1 The ePWM2 module is clocked by the system clock (SYSCLKOUT).

(1)

This register is EALLOW protected. See Section 5.2 for more information.

(2)

If a peripheral block is not used, the clock to that peripheral can be turned off to minimize power consumption.

(3)

To start the ePWM Time-base clock (TBCLK) within the ePWM modules, the TBCLKSYNC bit in PCLKCR0 must also be set.

SPRUFB0C – September 2007 – Revised May 2009 Clocking 41

Submit Documentation Feedback

Loading...

Loading...