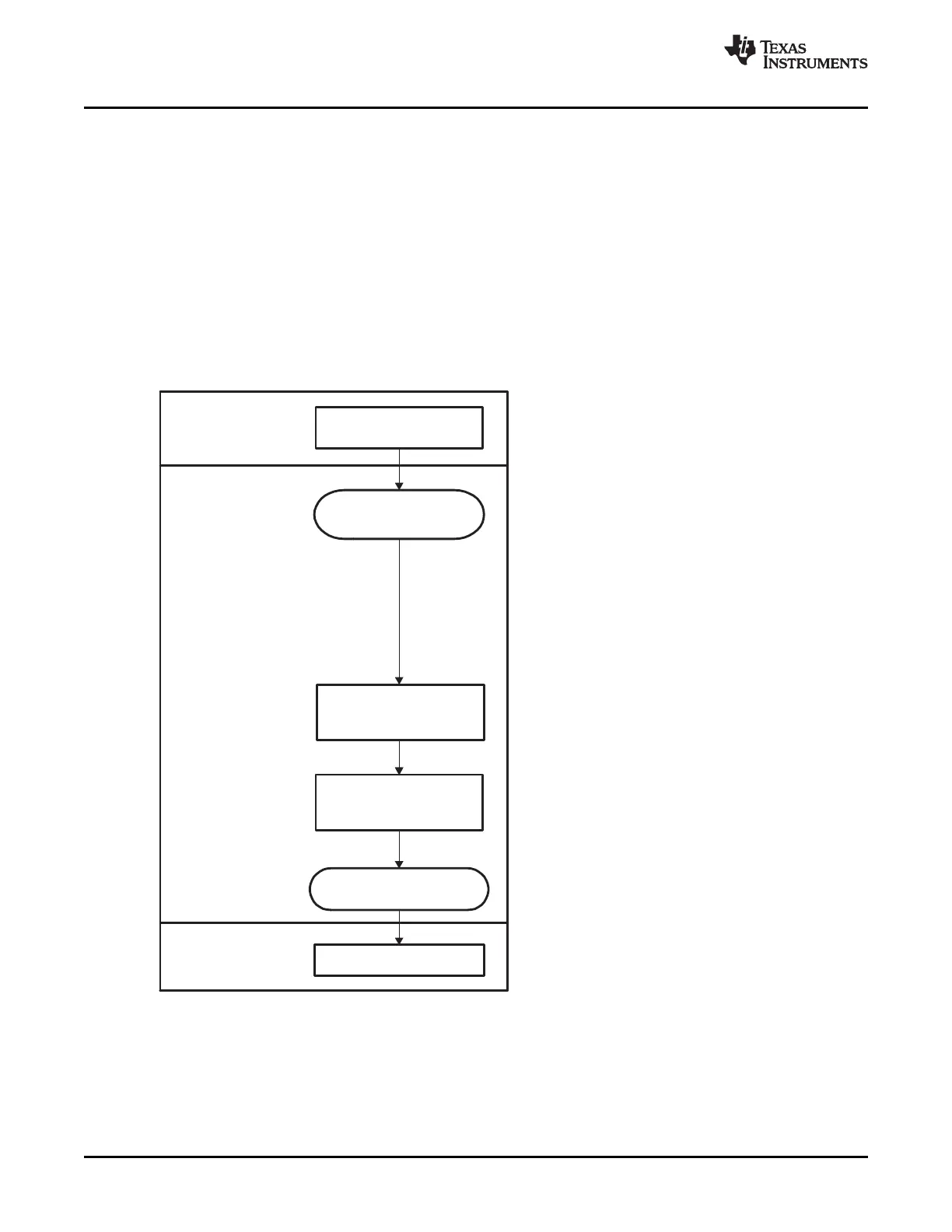

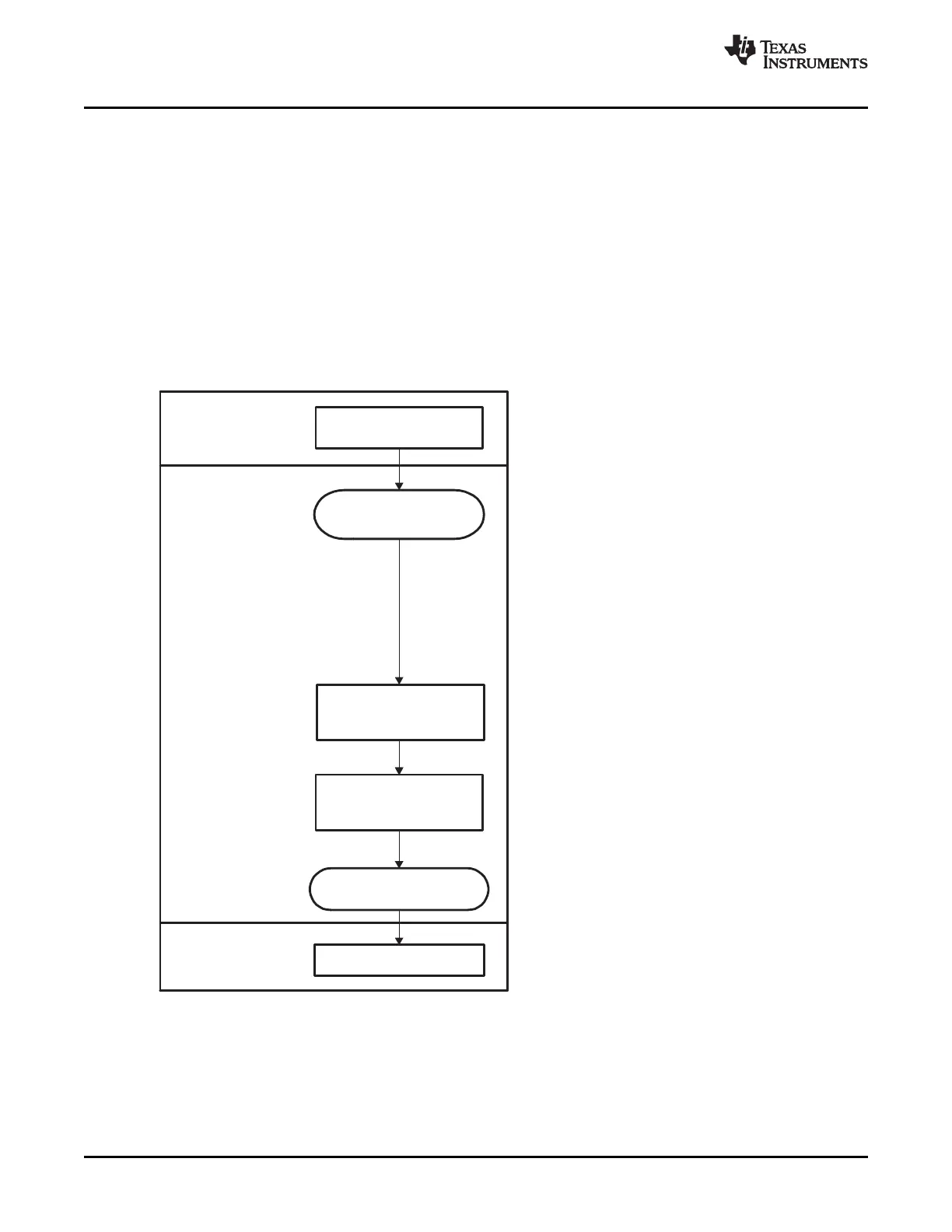

1.2.4 Procedure to Change the Flash Configuration Registers

Wait eight cycles to let the write instructions

propagate through the CPU pipeline. This

must be done before the return-from-function

call is made.

Write instructions to FOPT, FBANKWAIT,

etc.

The function that changes the configuration

cannot execute from the Flash or OTP.

Branch or call is required to properly flush the

CPU pipeline before the configuration

change.

Wait 8 cycles (8 NOPs)

Return to calling function

Continue execution

SARAM, Flash,

or OTP

Flash configuration

change

Do not execute from

Flash/OTP

SARAM

Begin Flash configuration

change

SARAM, Flash, OTP

Branch or call to

configuration code

Flash and OTP Power Modes

www.ti.com

2. For code security operation, all addresses between 0x33 FF80 and 0x33 FFF5 cannot be used for

program code or data, but must be programmed to 0x0000 when the Code Security Password is

programmed. If security is not a concern, addresses 0x33 FF80 through 0x33 FFF5 may be used for

code or data. See Chapter 2 for information in using the Code Security Module.

3. Addresses from 0x33 FFF0 to 0x33 FFF5 are reserved for data variables and should not contain

program code.

During flash configuration, no accesses to the flash or OTP can be in progress. This includes instructions

still in the CPU pipeline, data reads, and instruction pre-fetch operations. To be sure that no access takes

place during the configuration change, you should follow the procedure shown in Figure 1-3 for any code

that modifies the FOPT, FPWR, FBANKWAIT, or FOTPWAIT registers.

Figure 1-3. Flash Configuration Access Flow Diagram

20 Flash and OTP Memory Blocks SPRUFB0C – September 2007 – Revised May 2009

Submit Documentation Feedback

Loading...

Loading...