www.ti.com

PIE Interrupt Registers

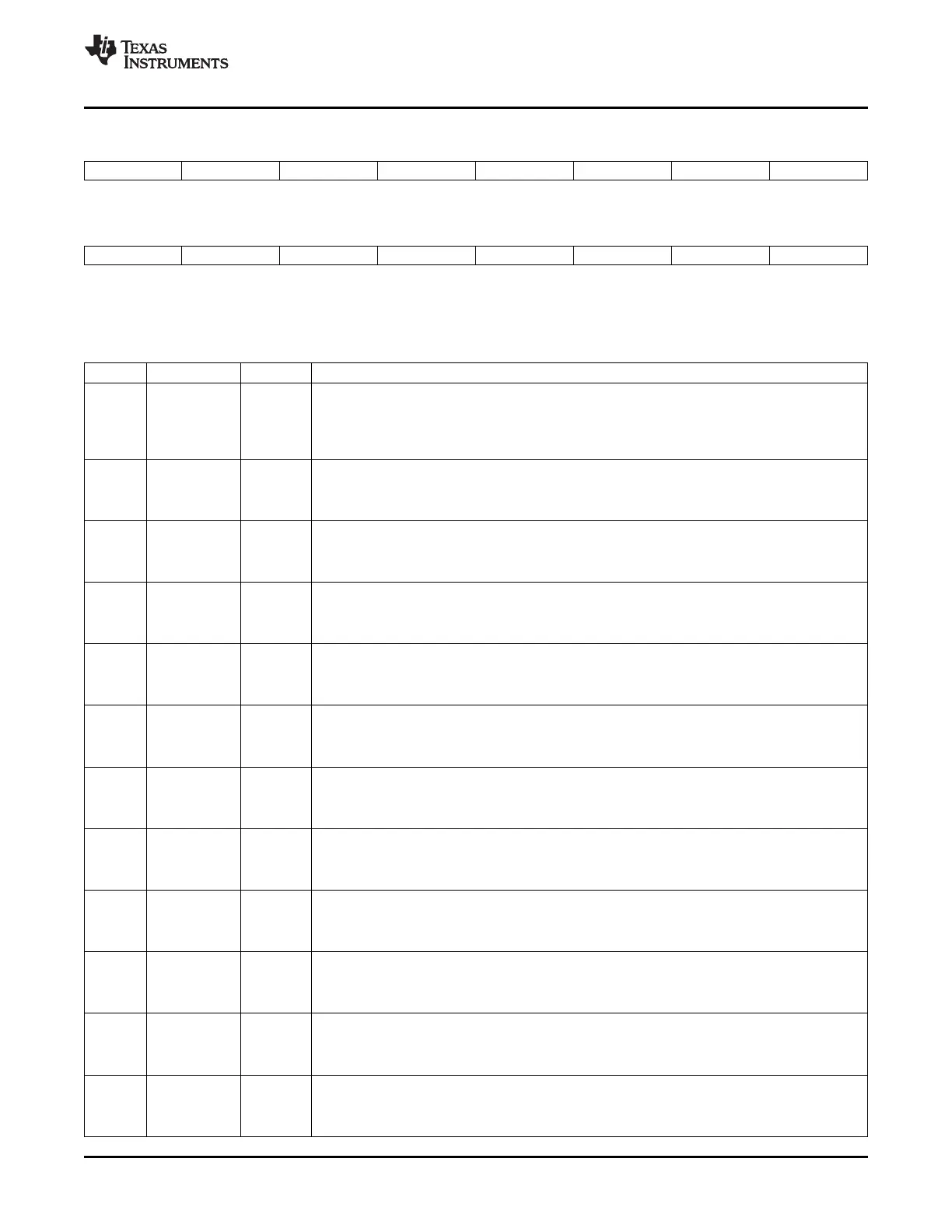

Figure 6-12. Interrupt Enable Register (IER) — CPU Register

15 14 13 12 11 10 9 8

RTOSINT DLOGINT INT14 INT13 INT12 INT11 INT10 INT9

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

7 6 5 4 3 2 1 0

INT8 INT7 INT6 INT5 INT4 INT3 INT2 INT1

R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; - n = value after reset

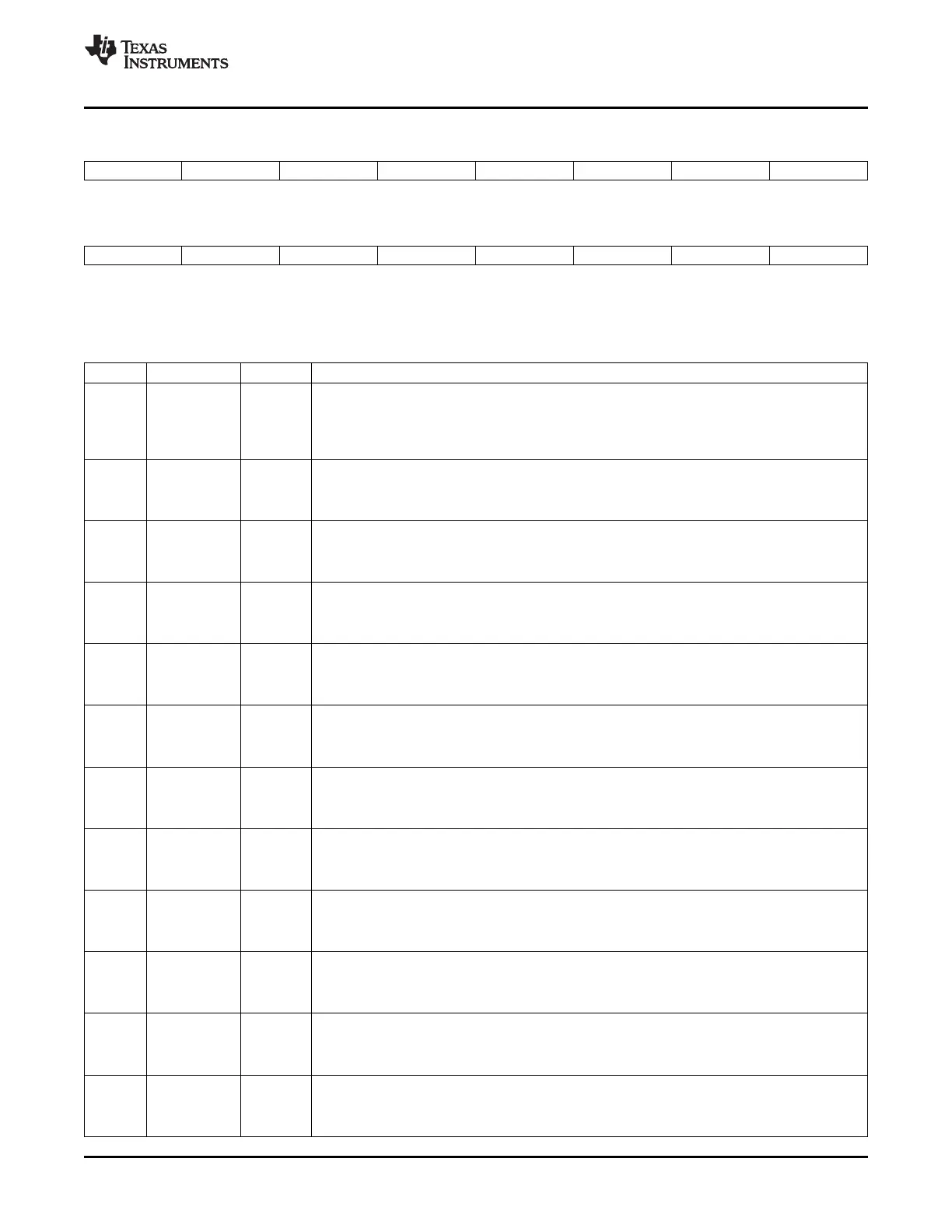

Table 6-12. Interrupt Enable Register (IER) — CPU Register Field Descriptions

Bits Field Value Description

15 RTOSINT Real-time operating system interrupt enable. RTOSINT enables or disables the CPU RTOS

interrupt.

0 Level INT6 is disabled

1 Level INT6 is enabled

14 DLOGINT Data logging interrupt enable. DLOGINT enables or disables the CPU data logging interrupt.

0 Level INT6 is disabled

1 Level INT6 is enabled

13 INT14 Interrupt 14 enable. INT14 enables or disables CPU interrupt level INT14.

0 Level INT14 is disabled

1 Level INT14 is enabled

12 INT13 Interrupt 13 enable. INT13 enables or disables CPU interrupt level INT13.

0 Level INT13 is disabled

1 Level INT13 is enabled

11 INT12 Interrupt 12 enable. INT12 enables or disables CPU interrupt level INT12.

0 Level INT12 is disabled

1 Level INT12 is enabled

10 INT11 Interrupt 11 enable. INT11 enables or disables CPU interrupt level INT11.

0 Level INT11 is disabled

1 Level INT11 is enabled

9 INT10 Interrupt 10 enable. INT10 enables or disables CPU interrupt level INT10.

0 Level INT10 is disabled

1 Level INT10 is enabled

8 INT9 Interrupt 9 enable. INT9 enables or disables CPU interrupt level INT9.

0 Level INT9 is disabled

1 Level INT9 is enabled

7 INT8 Interrupt 8 enable. INT8 enables or disables CPU interrupt level INT8.

0 Level INT8 is disabled

1 Level INT8 is enabled

6 INT7 Interrupt 7 enable. INT7 enables or disables CPU interrupt level INT7.

0 Level INT7 is disabled

1 Level INT7 is enabled

5 INT6 Interrupt 6 enable. INT6 enables or disables CPU interrupt level INT6.

0 Level INT6 is disabled

1 Level INT6 is enabled

4 INT5 Interrupt 5 enable.INT5 enables or disables CPU interrupt level INT5.

0 Level INT5 is disabled

1 Level INT5 is enabled

SPRUFB0C – September 2007 – Revised May 2009 Peripheral Interrupt Expansion (PIE) 145

Submit Documentation Feedback

Loading...

Loading...