Register Bit Definitions

www.ti.com

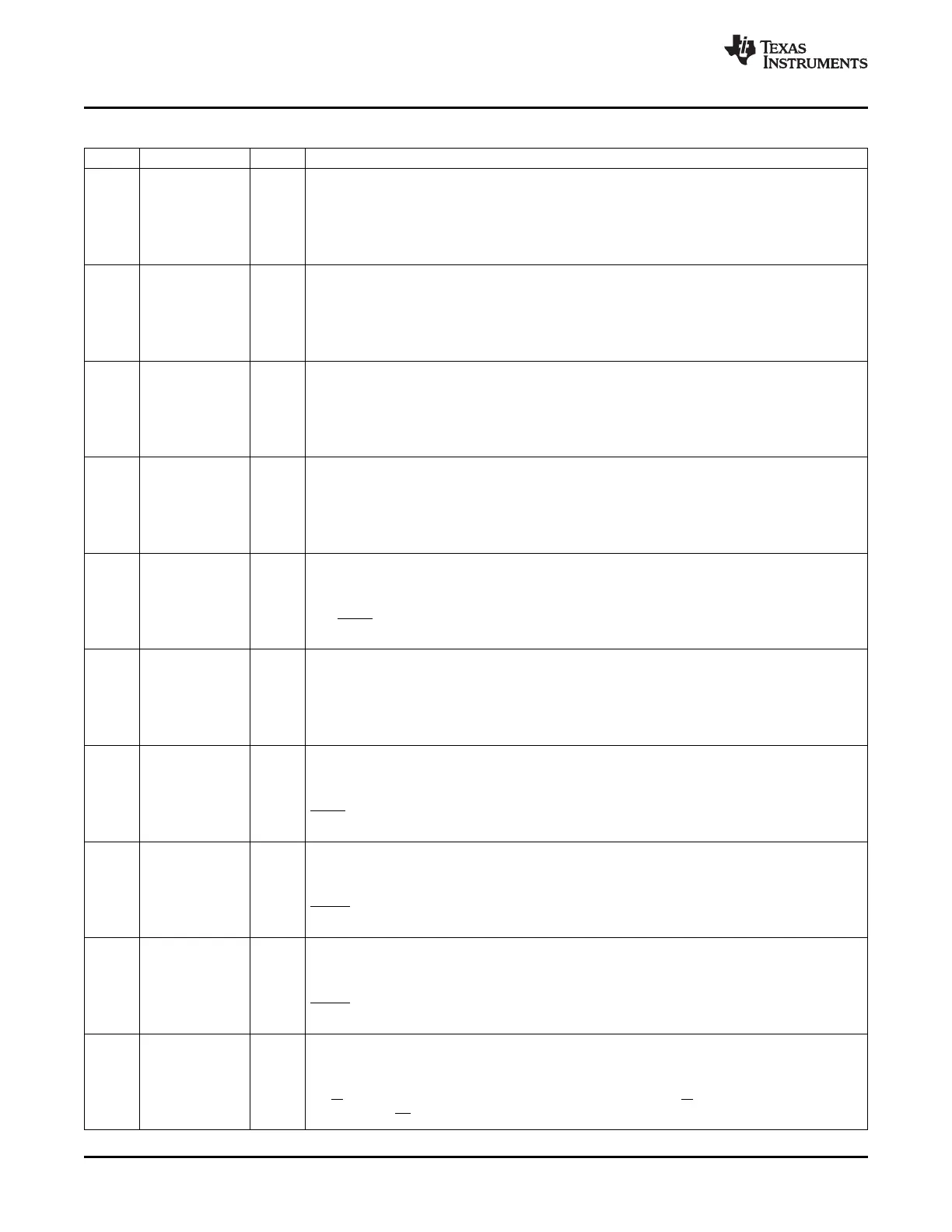

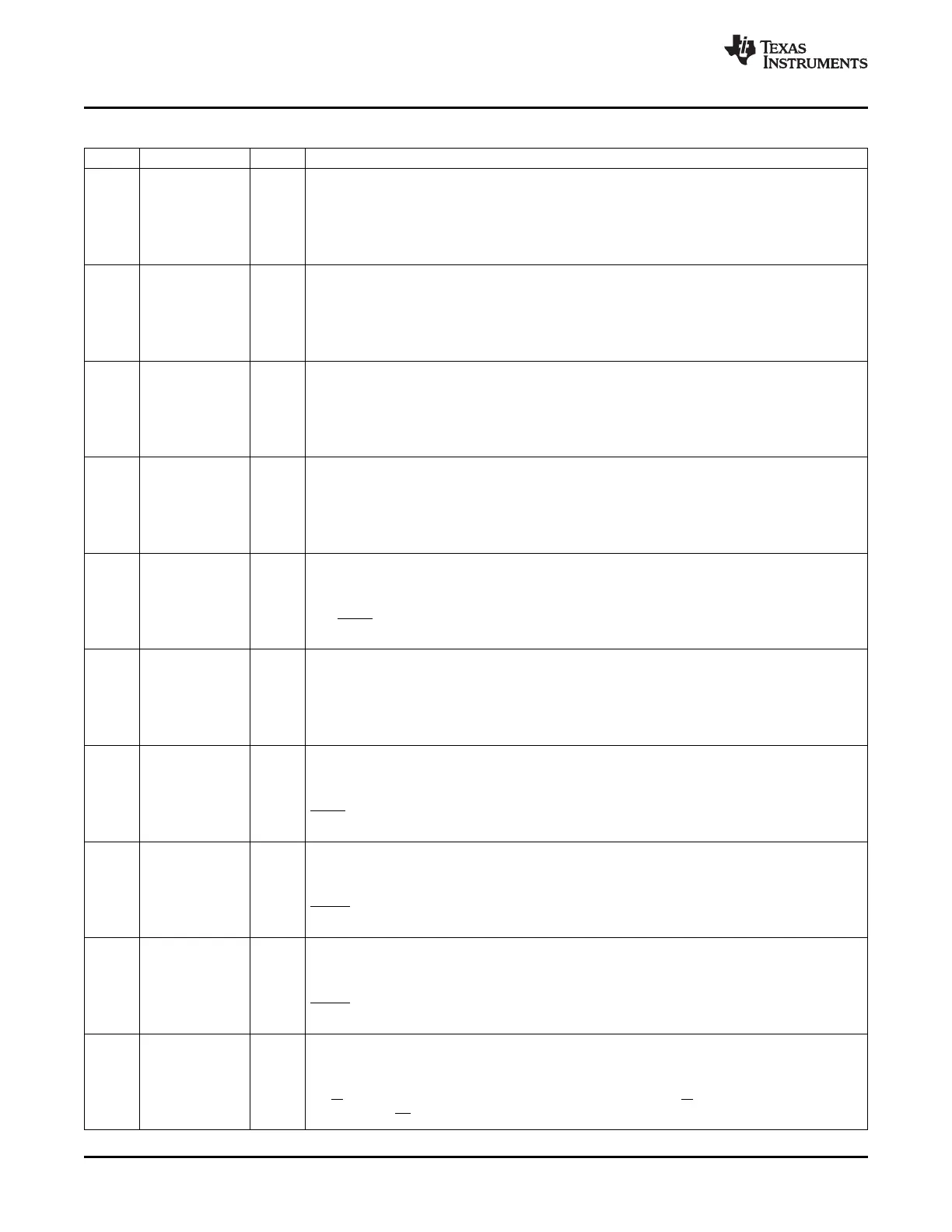

Table 4-14. GPIO Port B MUX 1 (GPBMUX1) Register Field Descriptions (continued)

Bit Field Value Description

25:24 GPIO44 Configure this pin:

00 GPIO 44 - general purpose I/O 44 (default)

01 Reserved

10 or XA4 - External interface (XINTF) address line 4 (O)

11

23:22 GPIO43 Configure this pin as:

00 GPIO 43 - general purpose I/O 43 (default)

01 Reserved

10 or XA3 - External interface (XINTF) address line 3 (O)

11

21:20 GPIO42 Configure this pin as:

00 GPIO 42 - general purpose I/O 42 (default)

01 Reserved

10 or XA2 - External interface (XINTF) address line 2 (O)

11

19:18 GPIO41 Configure this pin as:

00 GPIO 41 - general purpose I/O 41 (default)

01 Reserved

10 or XA1 - External interface (XINTF) address line 1 (O)

11

17:16 GPIO40 Configure this pin as:

00 GPIO 40 - general purpose I/O 40 (default)

01 Reserved

10 or XA0/ XWE1 - External interface (XINTF) address line 1 or external interface write enable strobe 1

11 (O)

15:14 GPIO39 Configure this pin as:

00 GPIO 39 - general purpose I/O 39 (default)

01 Reserved

10 or XA16 - External interface (XINTF) address line 16 (O)

11

13:12 GPIO38 Configure this pin as:

00 GPIO 38 - general purpose I/O 38 (default)

01 Reserved

10 or XWE0 - External interface write enable strobe 0

11

11:10 GPIO37 Configure this pin as:

00 GPIO 37 - general purpose I/O 37 (default)

01 ECAP2 - Enhanced capture input/output 2 (I/O)

10 or XZCS7 - External interface zone 7 chip select (O)

11

9:8 GPIO36 Configure this pin as:

00 GPIO 36 - general purpose I/O 36 (default)

01 SCIRXDA - SCI-A receive data (I)

10 or XZCS0 - External interface zone 0 chip select (O)

11

7:6 GPIO35 Configure this pin as:

00 GPIO 35 - general purpose I/O 35 (default)

01 SCITXDA - SCI-A transmit data (O)

10 or XR/ W - Read Not Write Strobe. Normally held high. When low, XR/ W indicates write cycle is active;

11 when high, XR/ W indicates read cycle is active.

88 General-Purpose Input/Output (GPIO) SPRUFB0C – September 2007 – Revised May 2009

Submit Documentation Feedback

Loading...

Loading...