Technology modules

D300529 0115 - BL67 I/O modules12-22

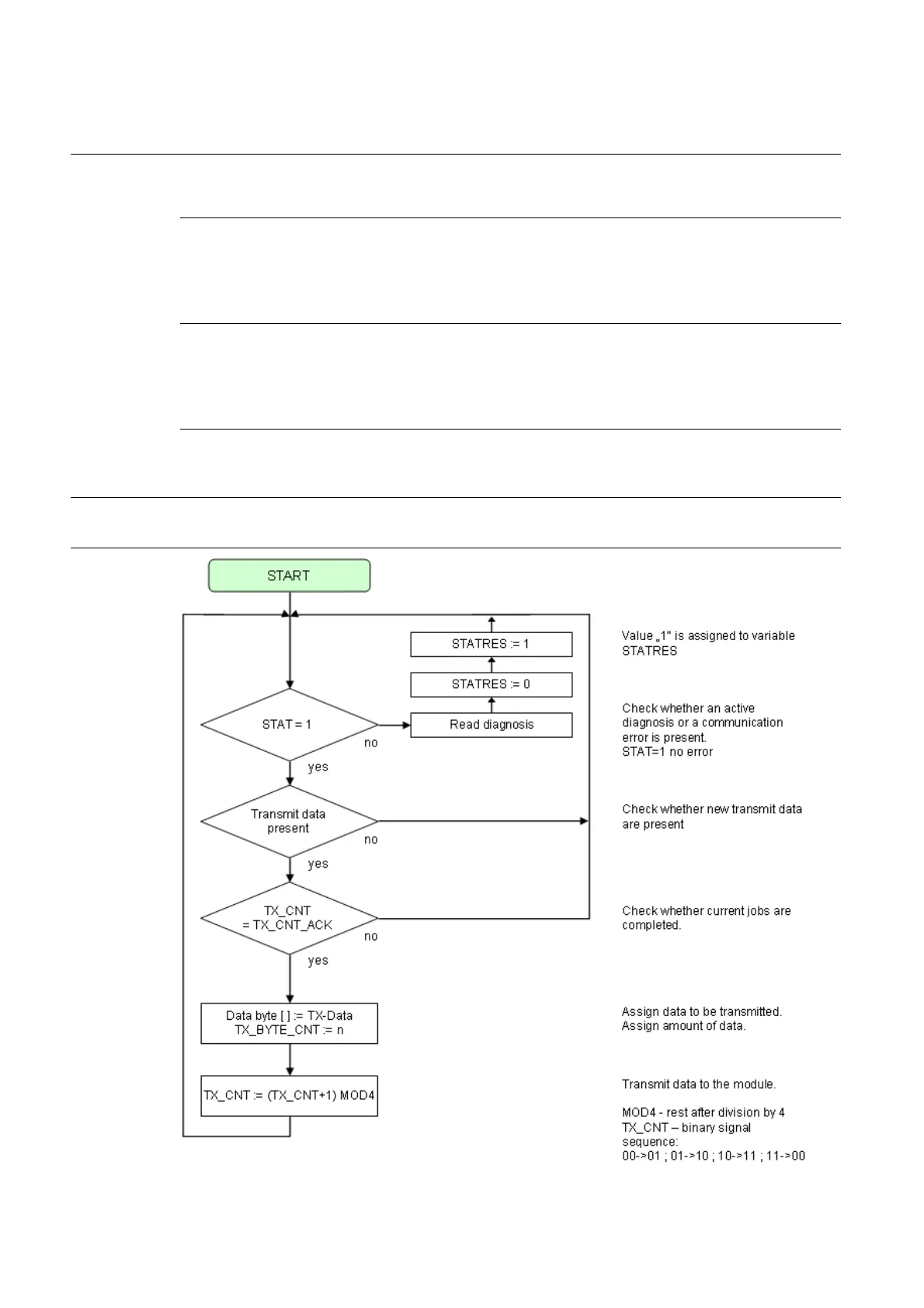

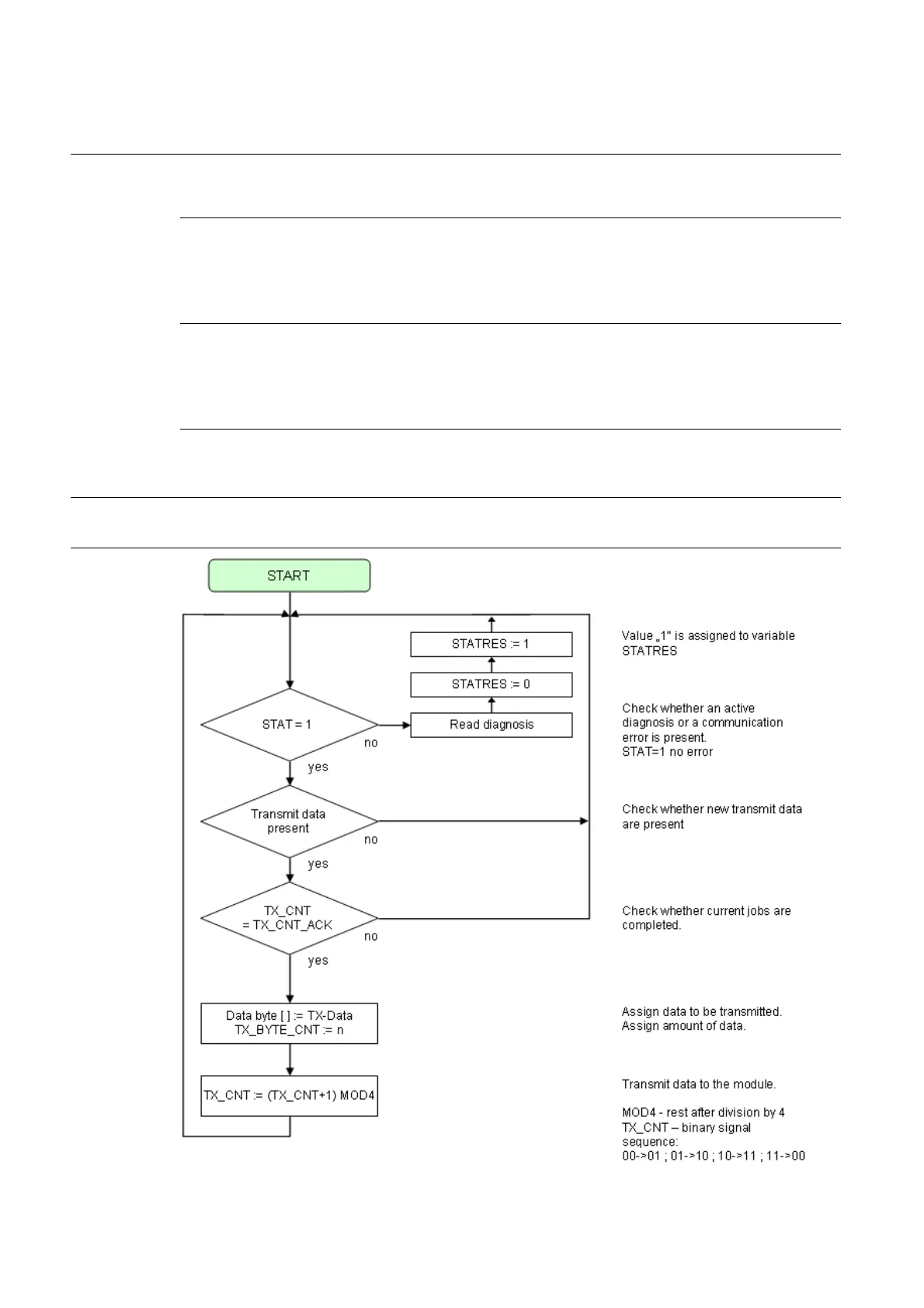

Schematic diagram of the transmit sequence

RXBUF FLUSH 0 - 1 The RXBUF FLUSH bit is used for clearing the receive buffer.

If STATRES = 0,1 or 0

→ 1:

A request with RXBUF FLUSH = 1 will be ignored.

If RXBUF FLUSH = 1, a rising edge 1

→0 at STATRES clears the

receive buffer.

TXBUF FLUSH 0-1 The TXBUF FLUSH bit is used for clearing the transmit buffer.

If STATRES = 0, 1 or 0

→1:

A request with TXBUF FLUSH = 1 will be ignored.

If TXBUF FLUSH = 1, a falling edge 1

→ 0 at STATRES clears the

transmit buffer.

TXBufDis 0-1 Setting this bit deactivates the sending of the TX buffer.

The bit can be used as control bit for actively triggering the sending

of the TX data buffer.

Figure 12-12:

Schematic dia-

gram of the trans-

mit sequence

Table 12-2:

Process output

data

Designation Value Description

Loading...

Loading...