13.3 Status Reports

13-28

IM GS210-01EN

13.3.2 Status Byte

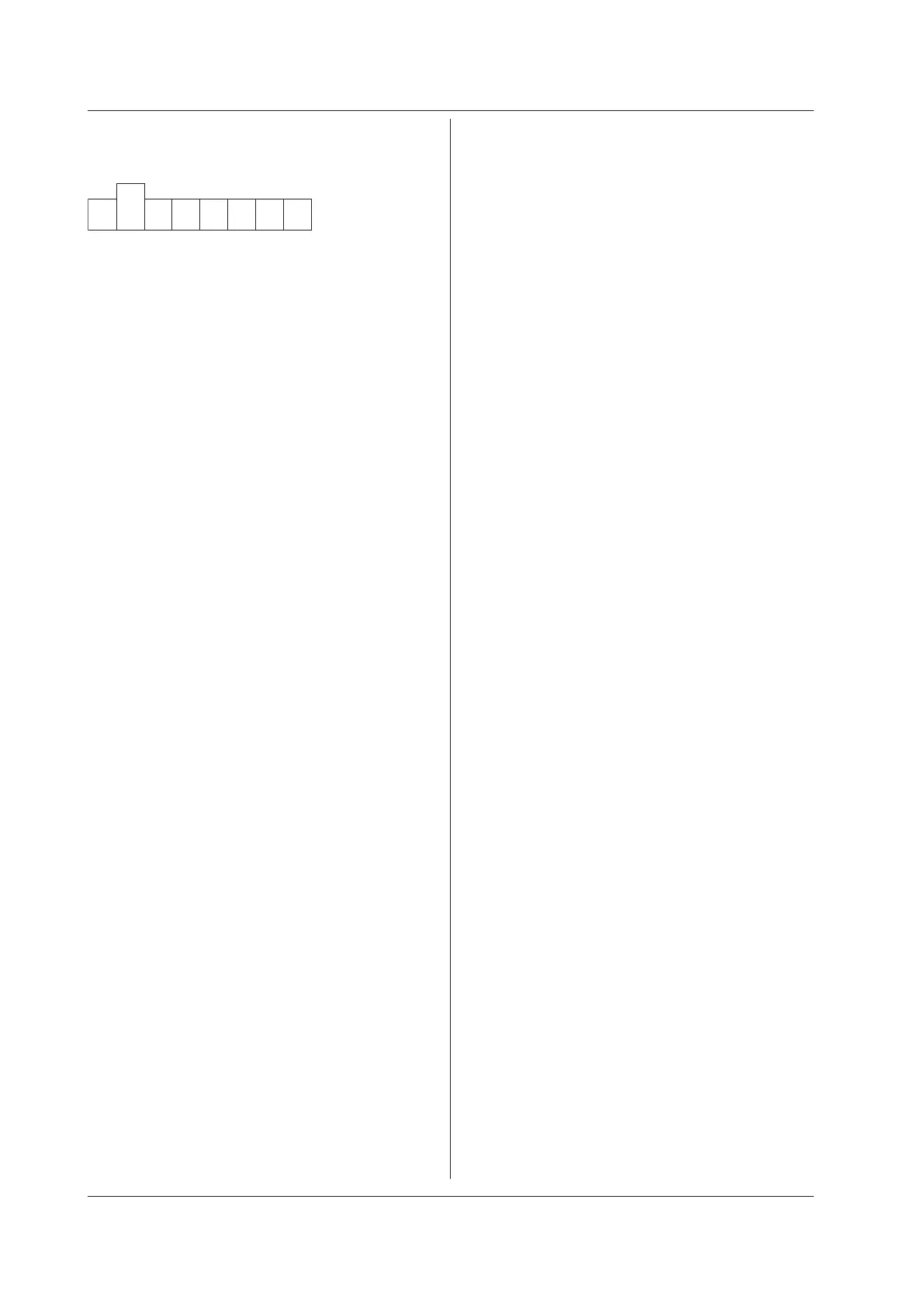

Status Byte

7 6 5 4 3 2 1 0

RQS

MSS ESB MAV EAV EES

Bits 0, 3, and 7

Not used (always 0)

Bit 1 EES (Extended Event Summary Bit)

This bit is set to 1 when the logical AND of the

extended event register and the extended event enable

register is 1. For details, see page 13-30.

Bit 2 EAV (Error Available)

This bit is set to 1 when the error queue is not empty.

For details, see page 13-31.

Bit 4 MAV (Message Available)

This bit is set to 1 when the output queue is not empty.

For details, see page 13-31.

Bit 5 ESB (Event Summary Bit)

This bit is set to 1 when the logical AND of the standard

event register and the standard event enable register

is 1. For details, see page 13-29.

Bit 6 RQS (Request Service)/MSS (Master

Status Summary)

This bit is set to 1 when the logical AND of the status

byte excluding bit 6 and the service request enable

register is 1. RQS is set to 1 when the MSS bit

changes from 0 to 1 and is cleared when serial polling

is carried out or when the MSS bit changes to 0.

Bit Masking

To mask a bit in the status byte so that it does not

cause an SRQ, set the corresponding bit of the service

request enable register to 0.

For example, to mask bit 2 (EAV) so that service is not

requested when an error occurs, set bit 2 of the service

request enable register to 0. Do this using the *SRE

command. To query whether each bit of the service

request enable register is 1 or 0, use *SRE?. For

details on the *SRE command, see section 13.2.11.

Status Byte Operation

A service request is issued when bit 6 in the status

byte becomes 1. Bit 6 is set to 1 when any other bit

becomes 1 (when the corresponding bit of the service

request enable register is also set to 1).

For example, if an event occurs and the logical OR

of a standard event register bit and its corresponding

enable register bit is 1, then bit 5 (ESB) is set to 1. At

this point, if bit 5 of the service request enable register

is 1, bit 6 (MSS) is set to 1, and the GS200 requests

service from the controller.

You can check what type of event occurred by reading

the contents of the status byte.

Reading the Status Byte

There are two ways to read the contents of the status

byte.

*STB? Query

Bit 6 functions as MSS when a query is made using

*STB?. This causes the MSS to be read. This query

does not cause any of the status byte bits to be cleared

after the status byte is read.

Serial Polling

Serial polling causes bit 6 to function as an RQS bit.

This causes the RQS to be read. After the status byte

is read, only the RQS bit is cleared. You cannot read

the MSS bit when serial polling is used.

Clearing the Status Byte

There is no way to clear all the bits in the status byte.

The bits that are cleared for each operation are shown

below.

*STB? Query

None of the bits are cleared.

Serial Polling

Only the RQS bit is cleared.

When a *CLS command is received

When a *CLS command is received, the status byte

itself is not cleared, but the contents of the standard

event register, which affects the bits in the status byte,

are cleared. As a result, the corresponding status

byte bits are cleared. Because the output queue is

not cleared with a *CLS command, bit 4 (MAV) in the

status byte is not affected. However, the output queue

will also be cleared if the *CLS command is received

just after a program message terminator.

Loading...

Loading...