Z8 Microcontrollers

Instruction Set ZiLOG

12-6 UM001601-0803

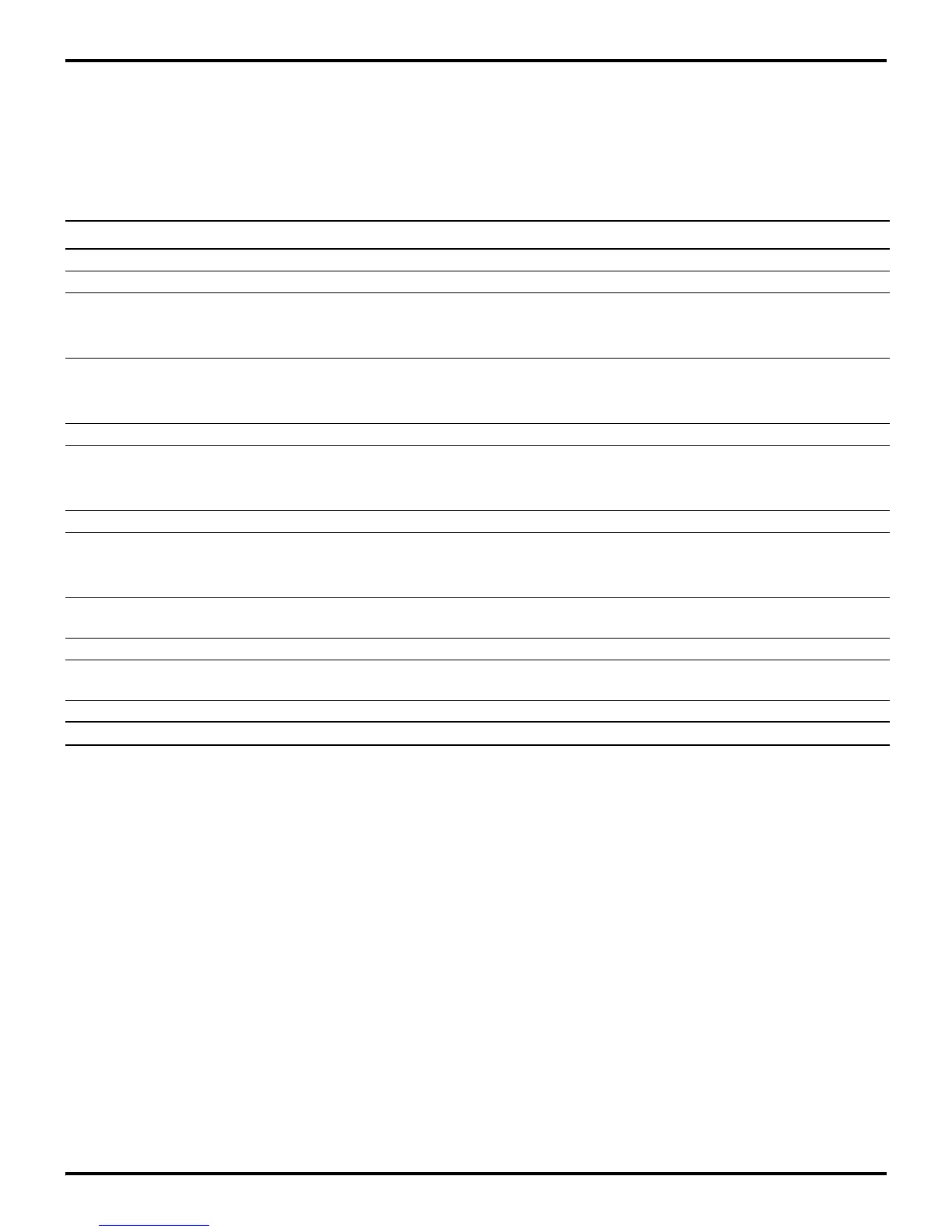

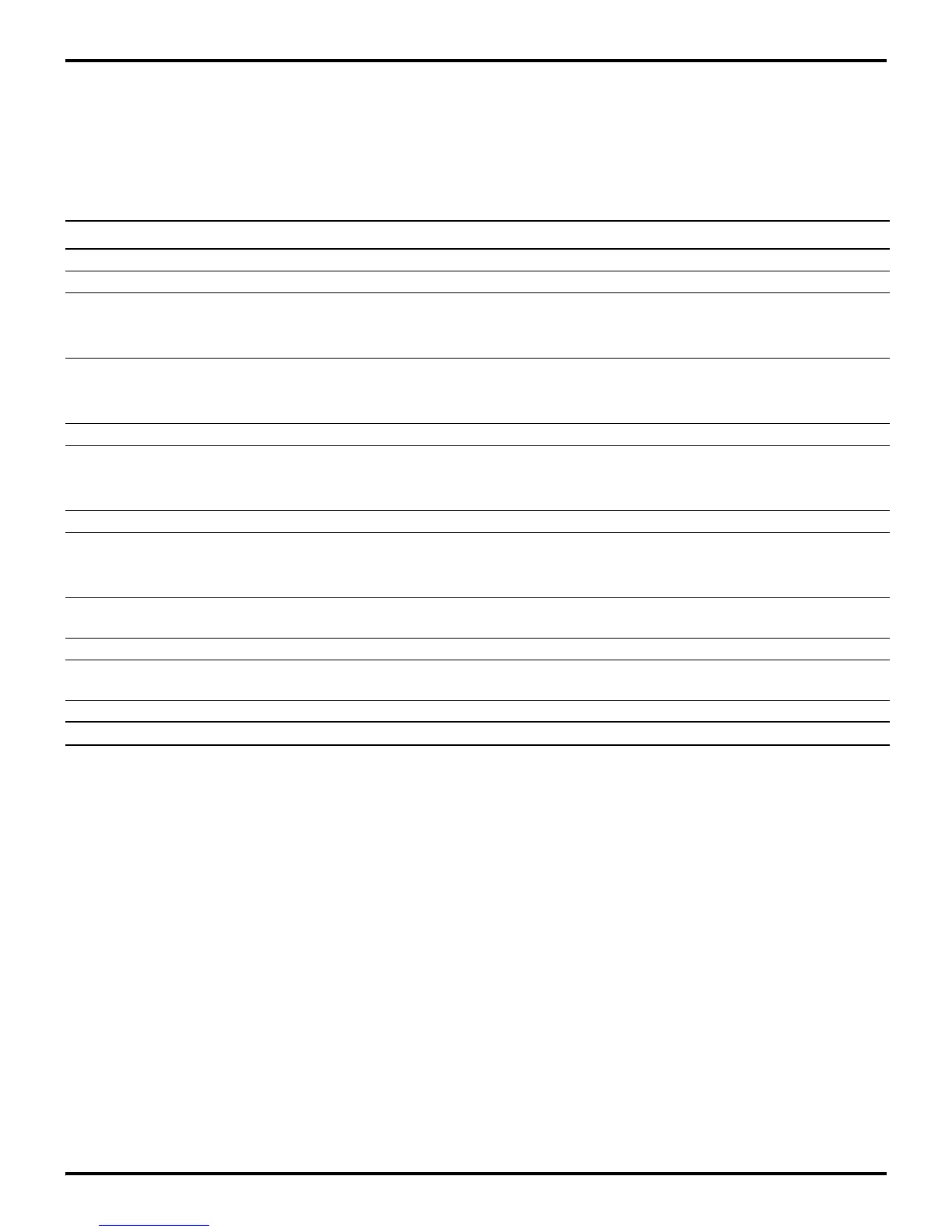

12.4 NOTATION AND BINARY ENCODING

In the detailed instruction descriptions that make up the rest of

this chapter, operands and status flags are represented by a nota

-

tional shorthand. Operands, condition codes, address modes, and

their notations are as follows (Table 12-12):

Tab le 12-12. Notational Shorthand

Notation Address Mode Operand Range *

cc Condition Code See condition codes

r Working Register Rn n = 0 – 15

R Register Reg Reg. represents a number in the range of 00H to FFH

or

Working Register Rn n = 0 – 15

RR Register Pair Reg Reg. represents an even number in the range of 00H to FEH

or

Working Register Pair RRp p = 0, 2, 4, 6, 8, 10, 12, or 14

Ir Indirect Working Register @Rn n = 0 –15

IR Indirect Register @Reg Reg. represents a number in the range of 00H to FFH

or

Indirect Working Register @Rn n = 0– 15

Irr Indirect Working Register Pair @RRp p = 0, 2, 4, 6, 8, 10, 12, or 14

IRR Indirect Register Pair @Reg Reg. represents an even number in the range 00H to FFH

or

Working Register Pair @RRp p = 0, 2, 4, 6, 8, 10, 12, or 14

X Indexed Reg (Rn) Reg. represents a number in the range of 00H to FFH and n = 0 – 15

DA Direct Address Addrs Addrs. represents a number in the range of 00H to FFH

RA Relative Address Addrs Addrs. represents a number in the range of +127 to –128 which is an

offset relative to the address of the next instruction

IM Immediate #Data Data is a number between 00H to FFH

*See the device product specification to determine the exact register file range available. The register file size varies by the device type.

Loading...

Loading...