A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 100 / 812

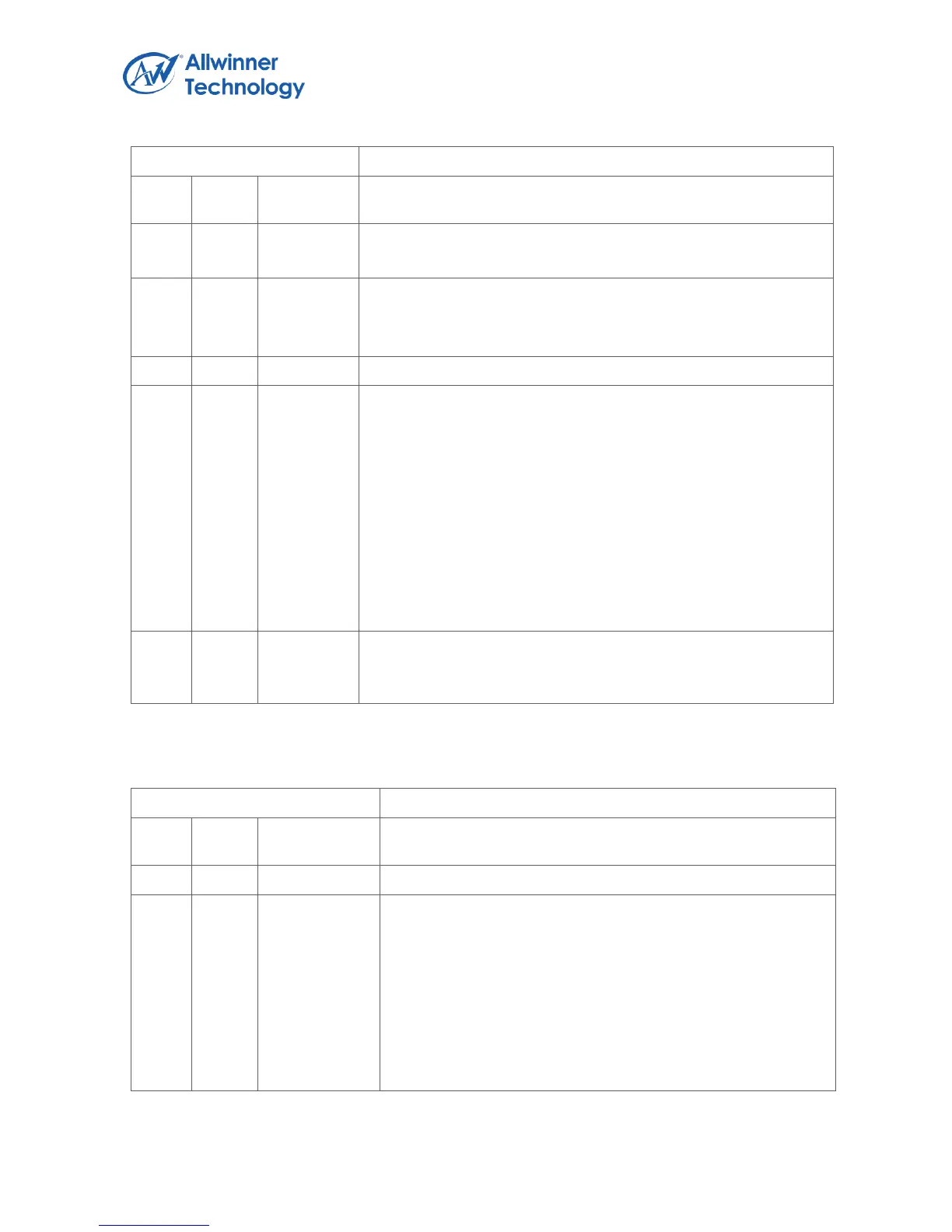

KEY_FIELD.

The bit[31:16] will be 0x1651 if bit15 is set, otherwise it will be 0.

VER_R_EN.

Version Reg Bit[31:16] Read Option Enable.

0: Disable, 1: Enable.

BOOT_SEL_PAD_STA.

BootSelect Pin Status

0: Low Level

1: High Level

The bit indicates current status of external BootSelect pin. In

default state, this pin is pull high by internal register and normal

boot is running. When this pin is drived to low level, normal boot

is bypassed and it would jump to USB for special application,

such as firmware update etc.

The status of BootSelect pin should be sampled by APB clock.

The debounce work is left for software.

VER_BITS.

This read-only bit field always reads back the mask revision level

of the chip.

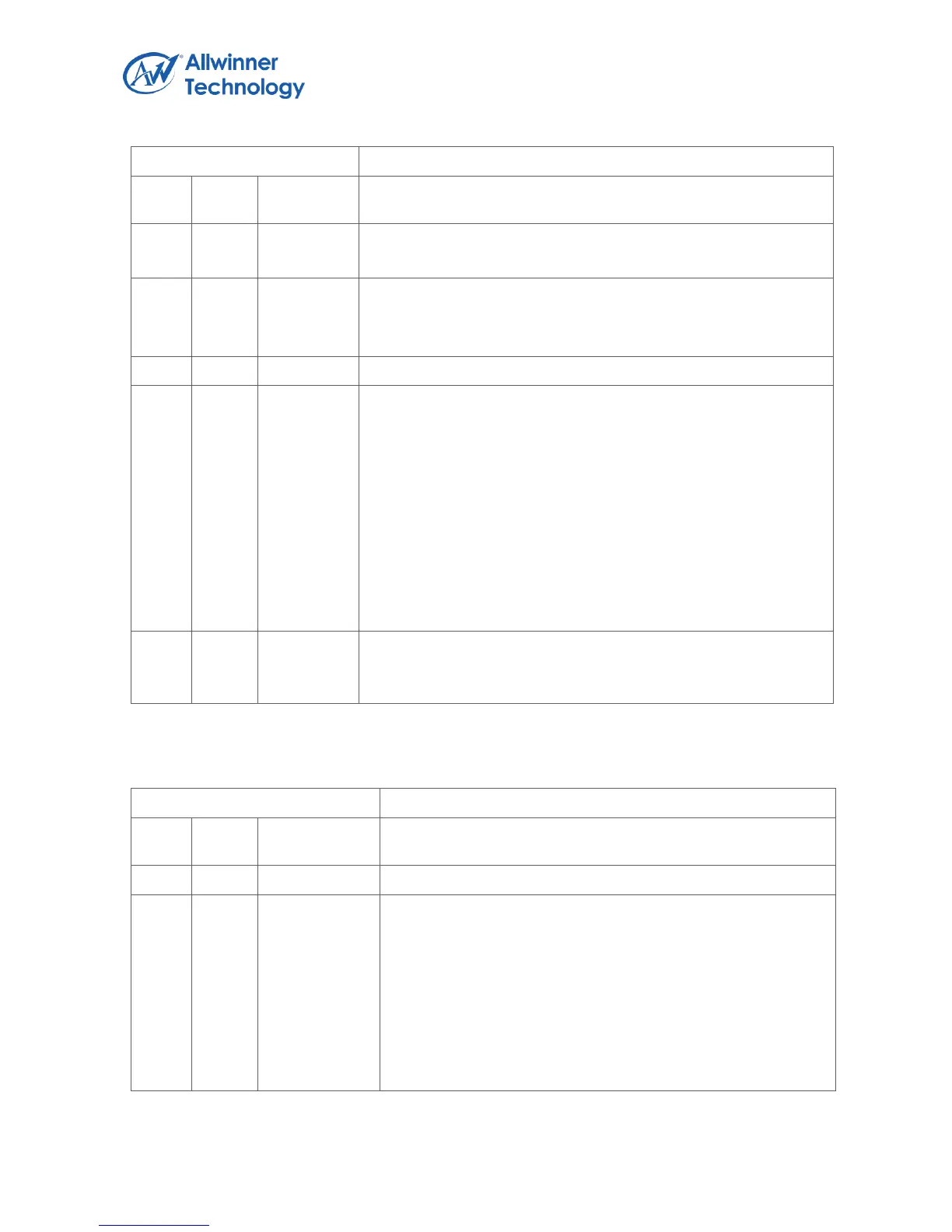

1.7.3.4. NMI INTERRUPT CONTROL REGISTER(DEFAULT: 0X00000000)

Register Name: NMI_IRQ_CTRL_REG

NMI_IRQ_SRC_TYPE.

External NMI Interrupt Source Type.

External NMI pin will be changed to alarm output if the power

of I/O is switched off, and it’s power source is RTCVDD.

00: Low level sensitive

01: Negative edge trigged

10: High level sensitive

11: Positive edge sensitive

Loading...

Loading...