A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 116 / 812

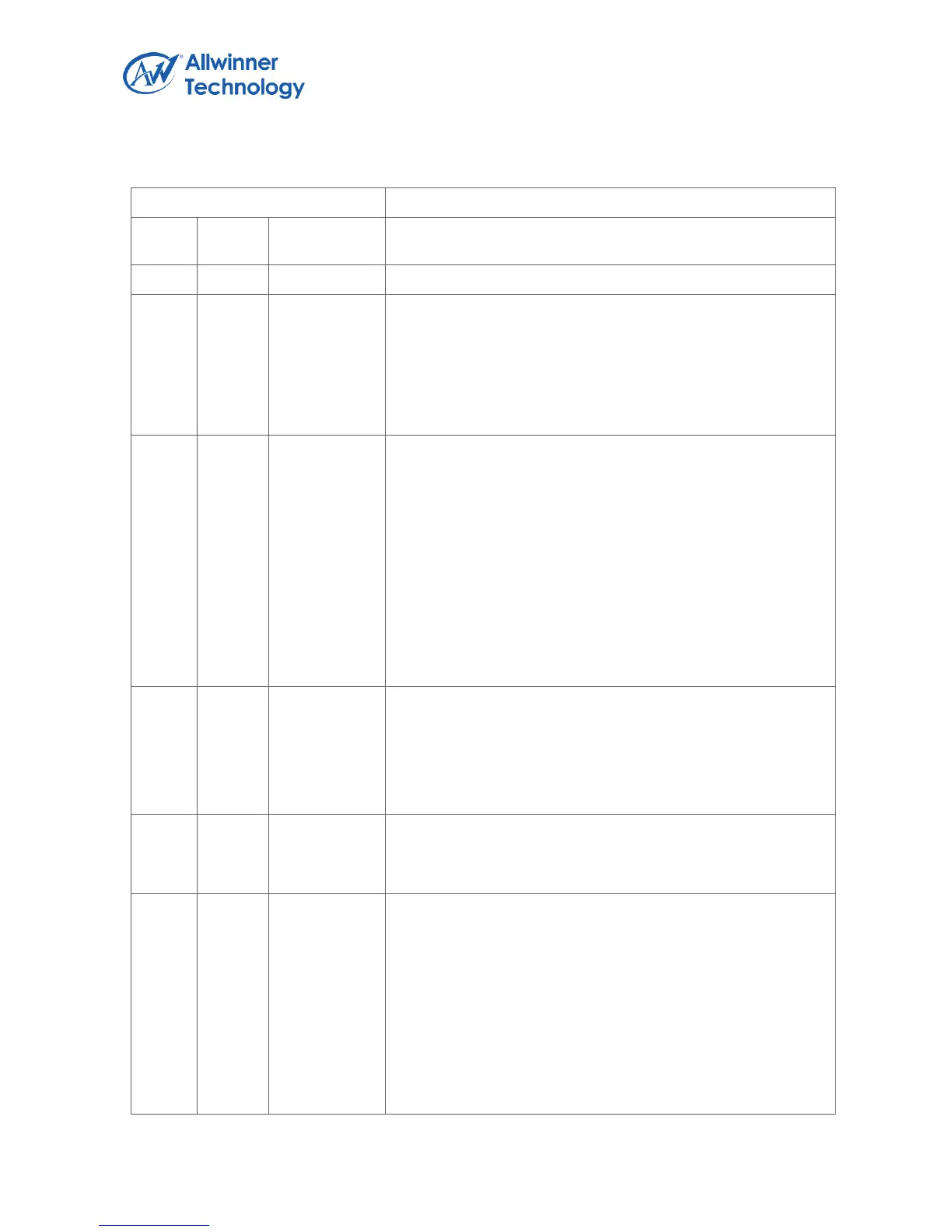

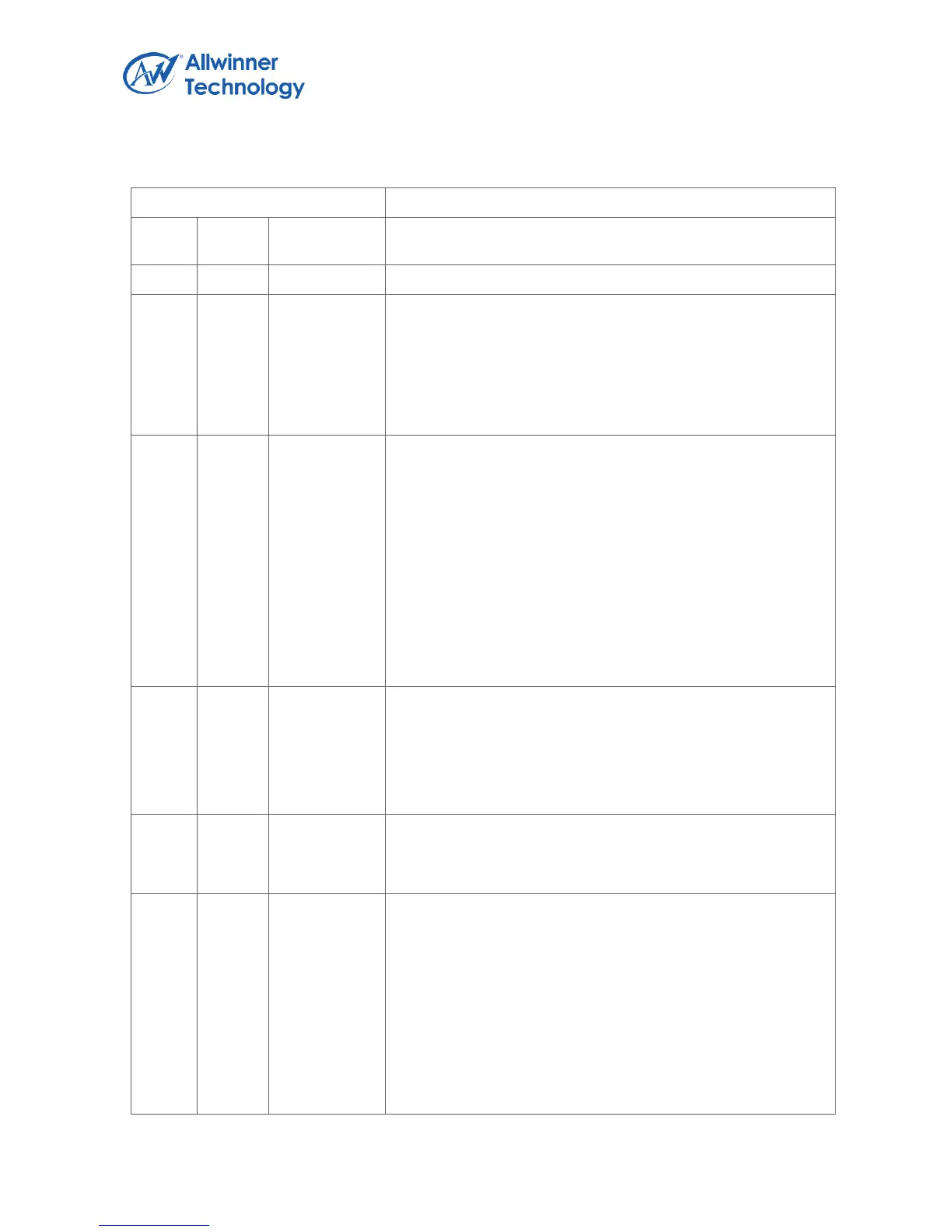

1.9.3.9. TIMER 2 CONTROL REGISTER(DEFAULT: 0X00000004)

Register Name: TMR2_CTRL_REG

TMR2_MODE.

Timer 2 mode.

0: Continuous mode. When interval value reached, the timer

will not disable automatically.

1: Single mode. When interval value reached, the timer will

disable automatically.

TMR2_CLK_PRES.

Select the pre-scale of timer 2 clock source.

000: /1

001: /2

010: /4

011: /8

100: /16

101: /32

110: /64

111: /128

TMR2_CLK_SRC.

Timer 2 Clock Source.

00: Low speed OSC,

01: OSC24M.

1x: /.

TMR2_RELOAD.

Timer 2 Reload.

0: No effect, 1: Reload timer 2 Interval value.

TMR2_EN.

Timer 2 Enable.

0: Stop/Pause, 1: Start.

If the timer is started, it will reload the interval value to

internal register, and the current counter will count from

interval value to 0.

If the current counter does not reach the zero, the timer

enable bit is set to “0”, the current value counter will pause.

At least wait for 2 Tcylces, the start bit can be set to 1.

In timer pause state, the interval value register can be

Loading...

Loading...