A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 156 / 812

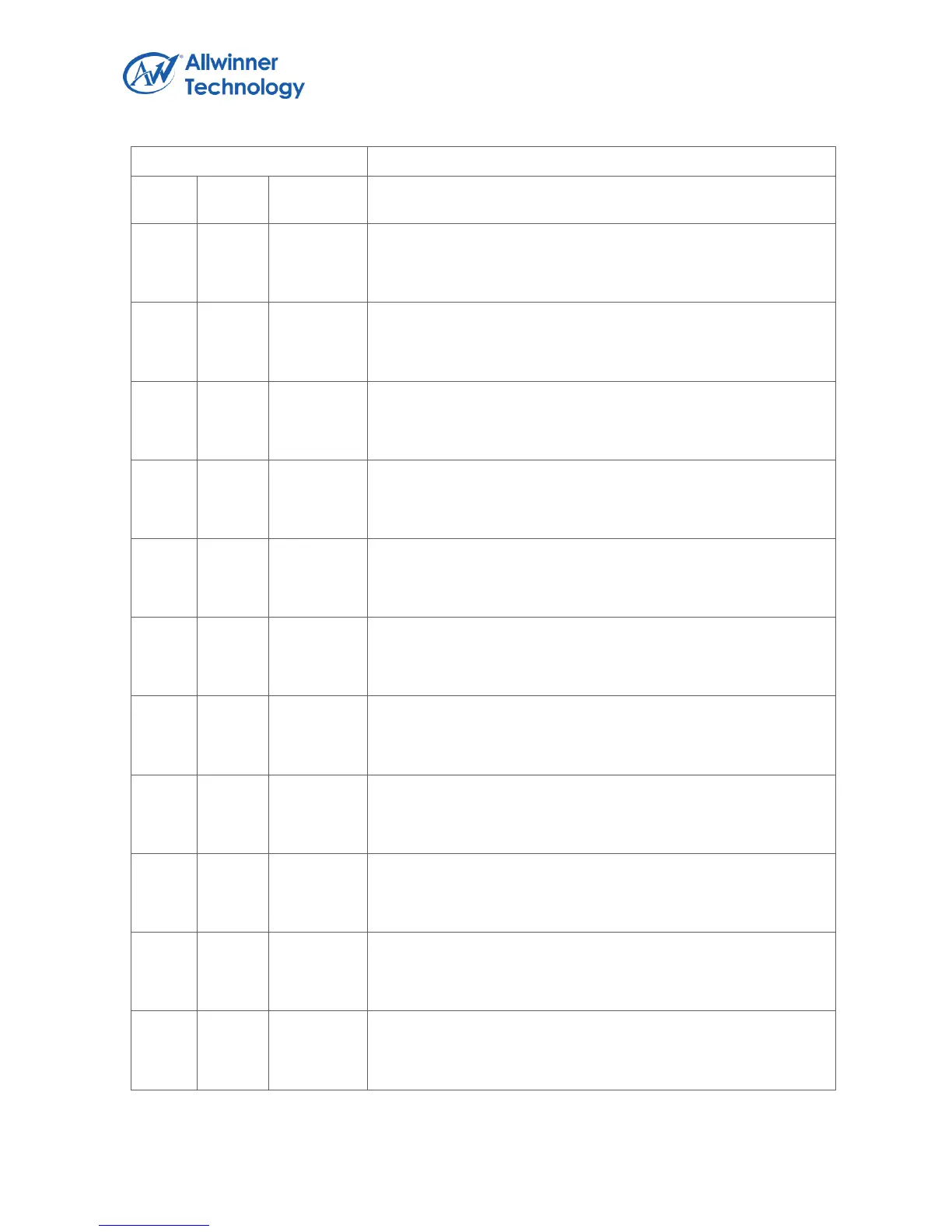

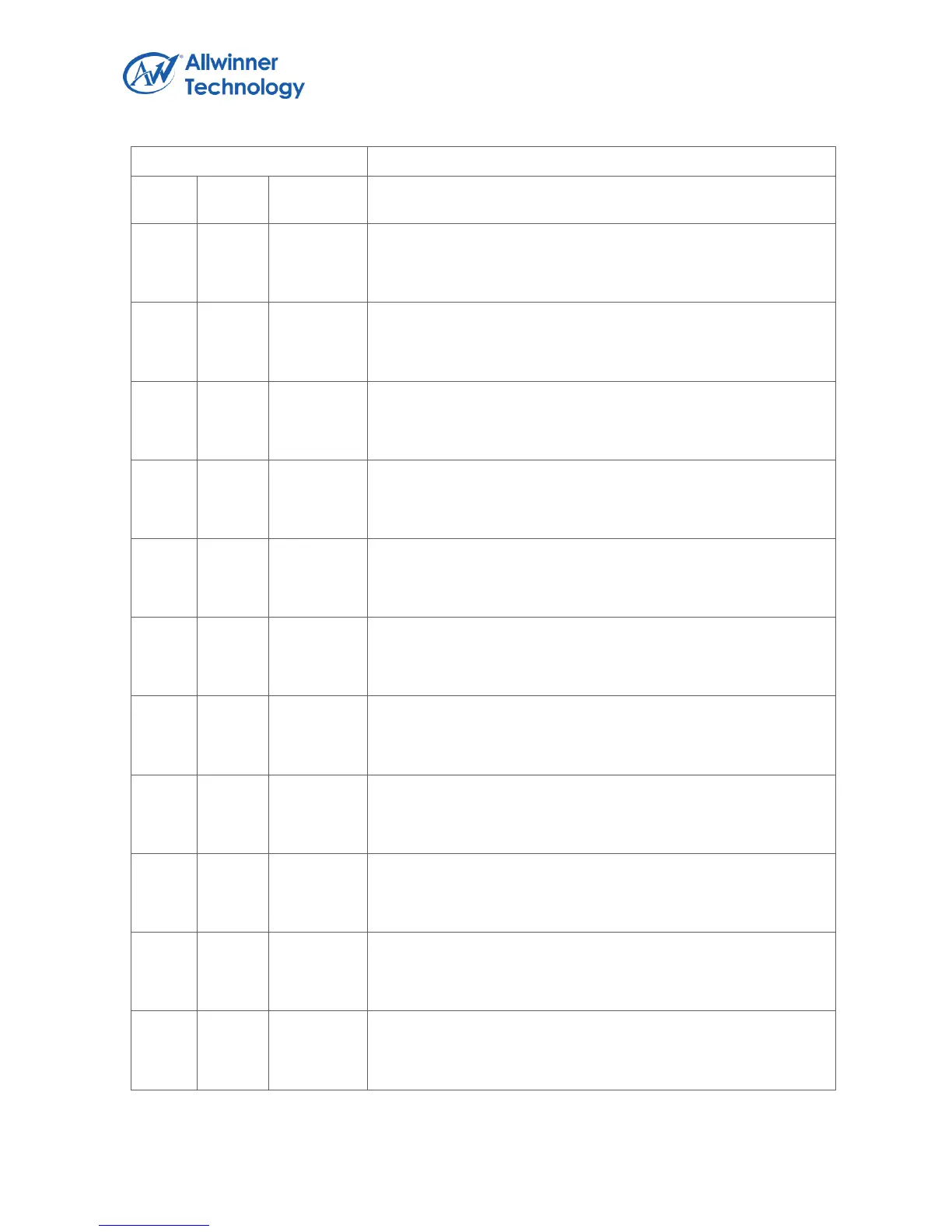

Register Name: DMA_IRQ_EN_REG

NDMA5_HF_IRQ_EN

Normal DMA 5 Half Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA4_END_IRQ_EN

Normal DMA 4 End Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA4_HF_IRQ_EN

Normal DMA 4 Half Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA3_END_IRQ_EN

Normal DMA 3 End Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA3_HF_IRQ_EN

Normal DMA 3 Half Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA2_END_IRQ_EN

Normal DMA 2 End Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA2_HF_IRQ_EN

Normal DMA 2 Half Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA1_END_IRQ_EN

Normal DMA 1 End Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA1_HF_IRQ_EN

Normal DMA 1 Half Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA0_END_IRQ_EN

Normal DMA 0 End Transfer Interrupt Enable.

0: Disable, 1: Enable.

NDMA0_HF_IRQ_EN

Normal DMA 0 Half Transfer Interrupt Enable.

0: Disable, 1: Enable.

Loading...

Loading...