A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 182 / 812

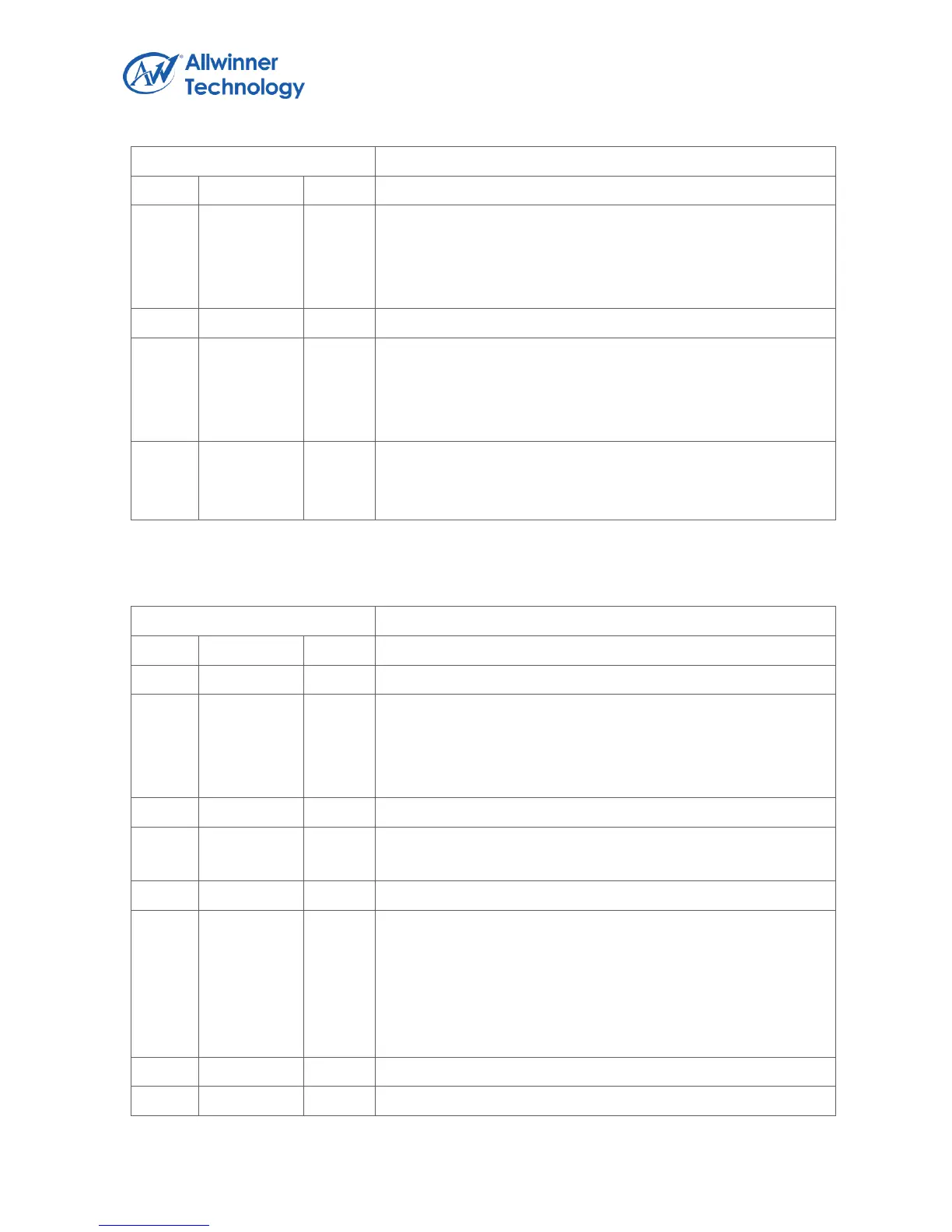

Register Name: AC_ADC_FIFOC

ADC_IRQ_EN.

ADC FIFO Data Available IRQ Enable.

0: Disable

1: Enable

ADC_OVERRUN_IRQ_EN.

ADC FIFO Over Run IRQ Enable

0: Disable

1: Enable

ADC_FIFO_FLUSH.

ADC FIFO Flush.

Write ‘1’ to flush TX FIFO, self clear to ‘0’.

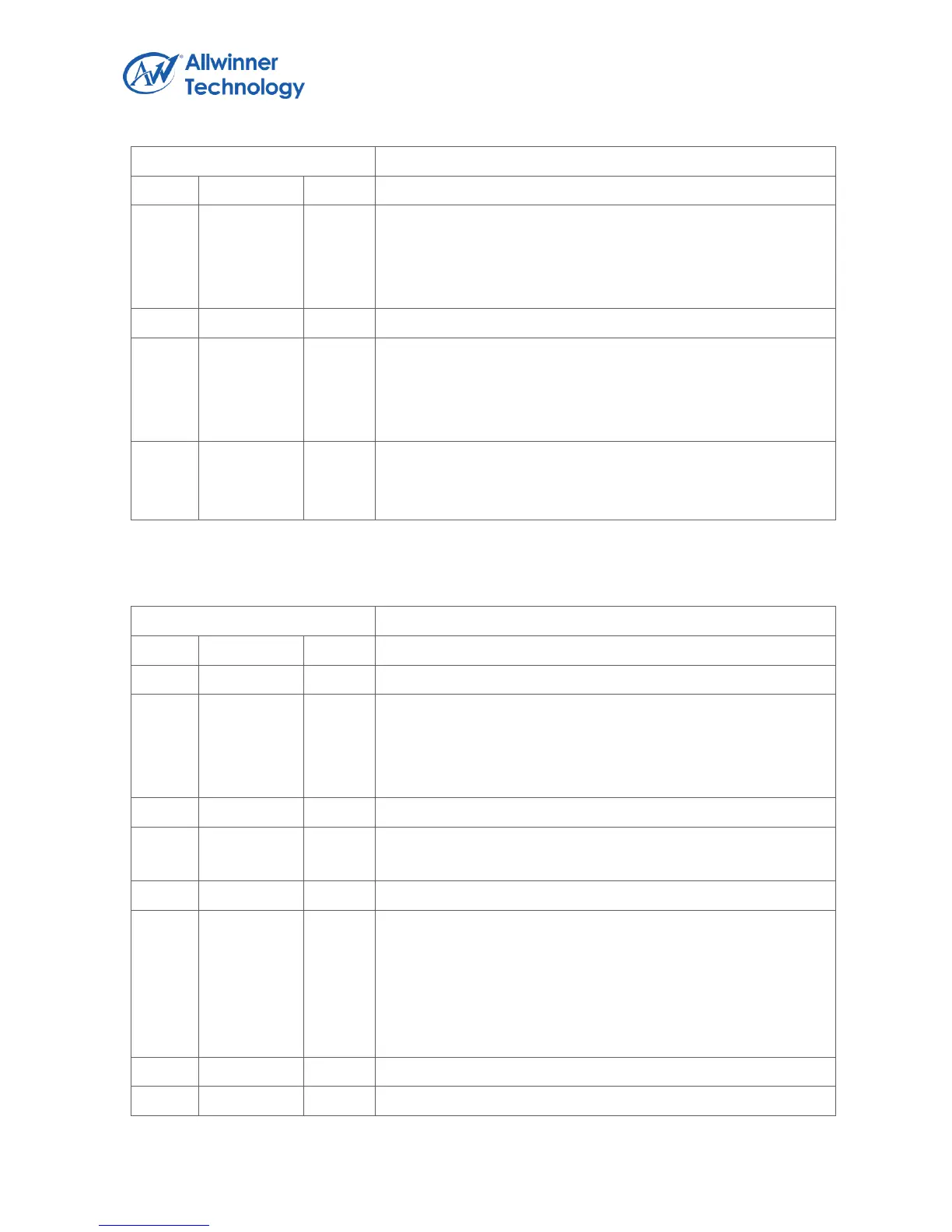

1.13.4.8. ADC FIFO STATUS REGISTER

Register Name: AC_ADC_FIFOS

RXA.

RX FIFO Available

0: No available data in RX FIFO

1: More than one sample in RX FIFO (>= 1 word)

RXA_CNT.

RX FIFO Available Sample Word Counter

RXA_INT.

RX FIFO Data Available Pending Interrupt

0: No Pending IRQ

1: Data Available Pending IRQ

Write ‘1’ to clear this interrupt or automatic clear if interrupt

condition fails.

Loading...

Loading...