A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 183 / 812

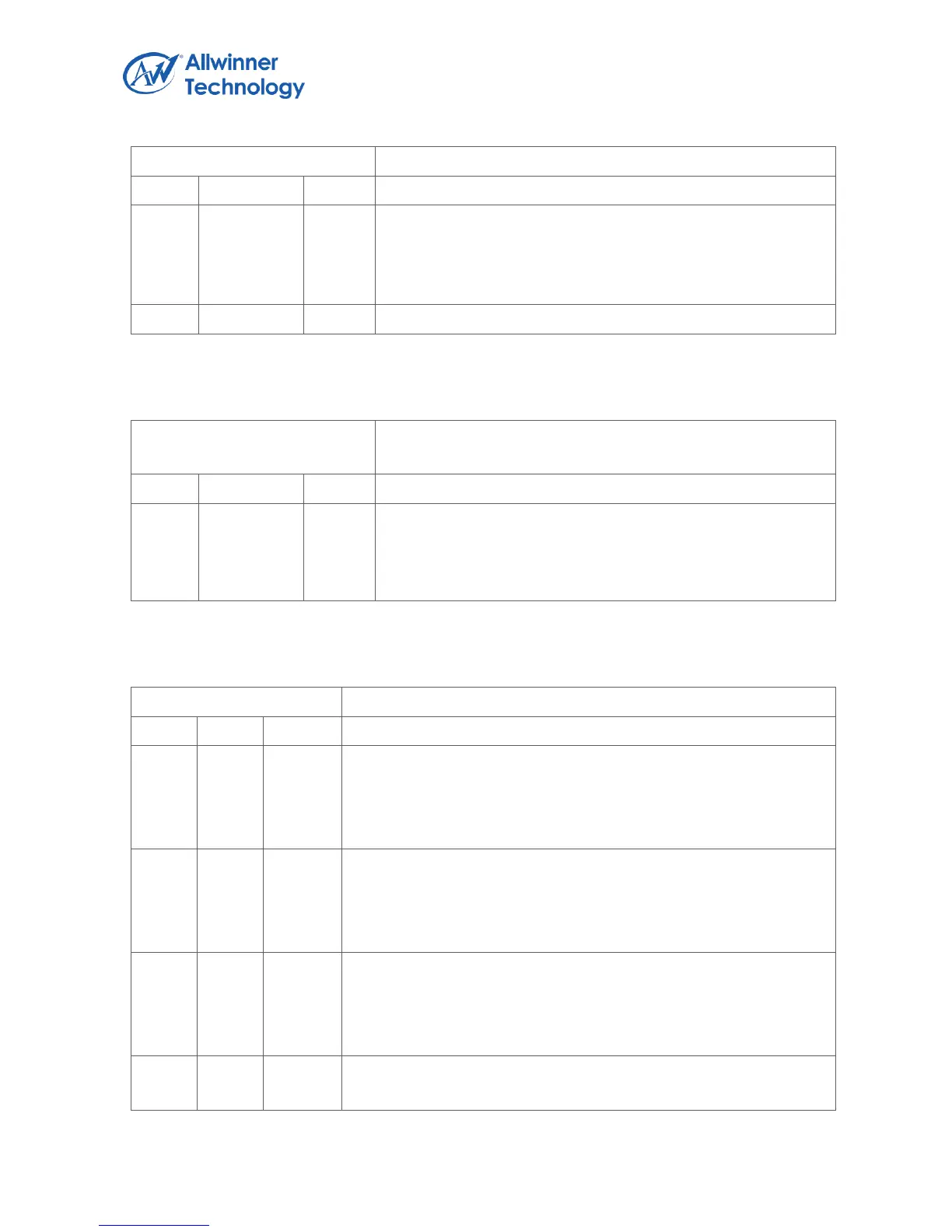

Register Name: AC_ADC_FIFOS

RX FIFO Overrun Pending Interrupt

0: No Pending IRQ

1: FIFO Overrun Pending IRQ

Write ‘1’ to clear this interrupt

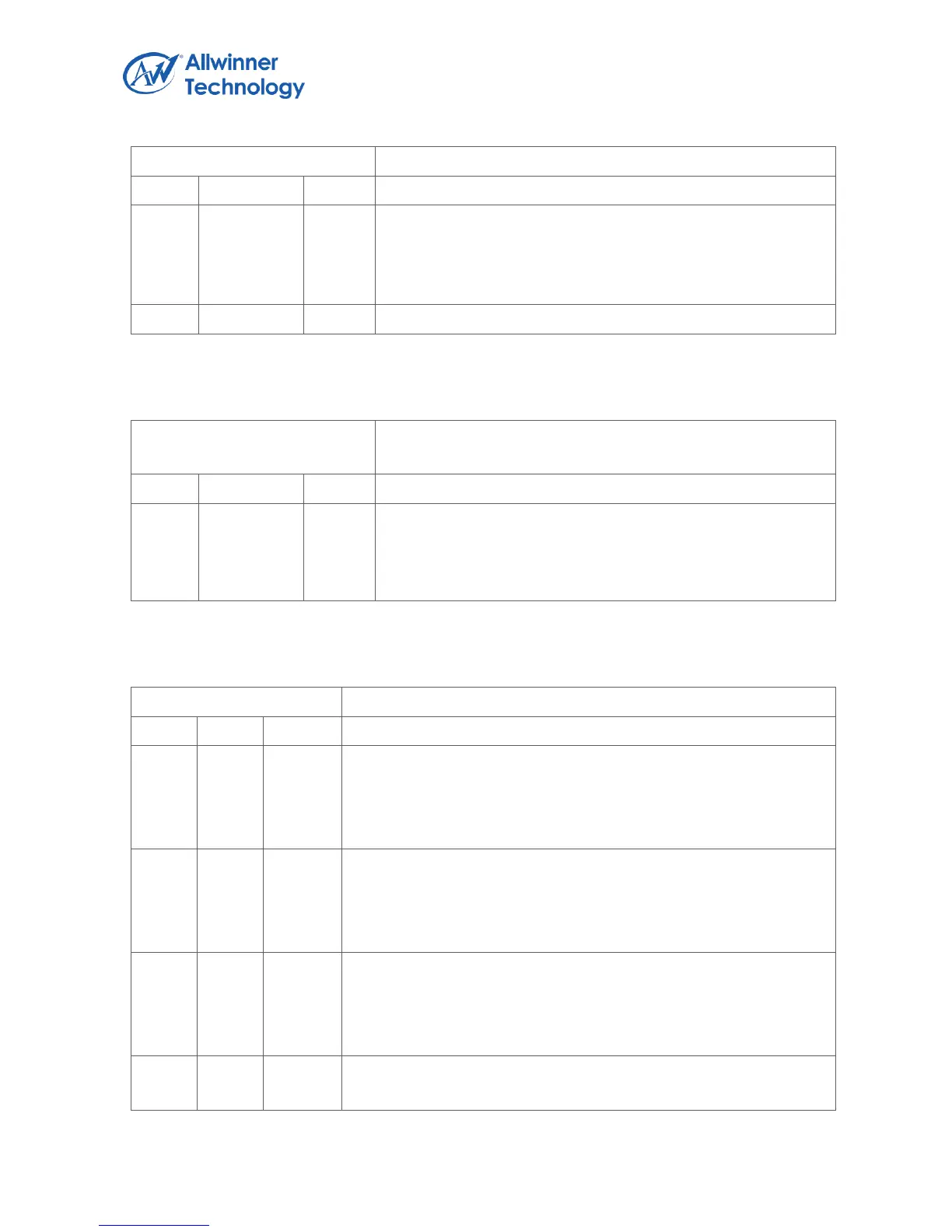

1.13.4.9. ADC RX DATA REGISTER

Register Name: AC_ADC_RXDATA

Default Value: 0x0000_0000

RX_DATA.

RX Sample

Host can get one sample by reading this register. The left

channel sample data is first and then the right channel sample.

1.13.4.10. ADC ANALOG CONTROL REGISTER

Register Name: AC_PA_ADC_ACTRL

ADCREN.

ADC Right Channel Enable

0-Disable

1-Enable

ADCLEN.

ADC Left Channel Enable

0-Disable

1-Enable

PREG1EN.

MIC1 pre-amplifier Enable

0-Disable

1-Enable

PREG2EN.

MIC2 pre-amplifier Enable

Loading...

Loading...