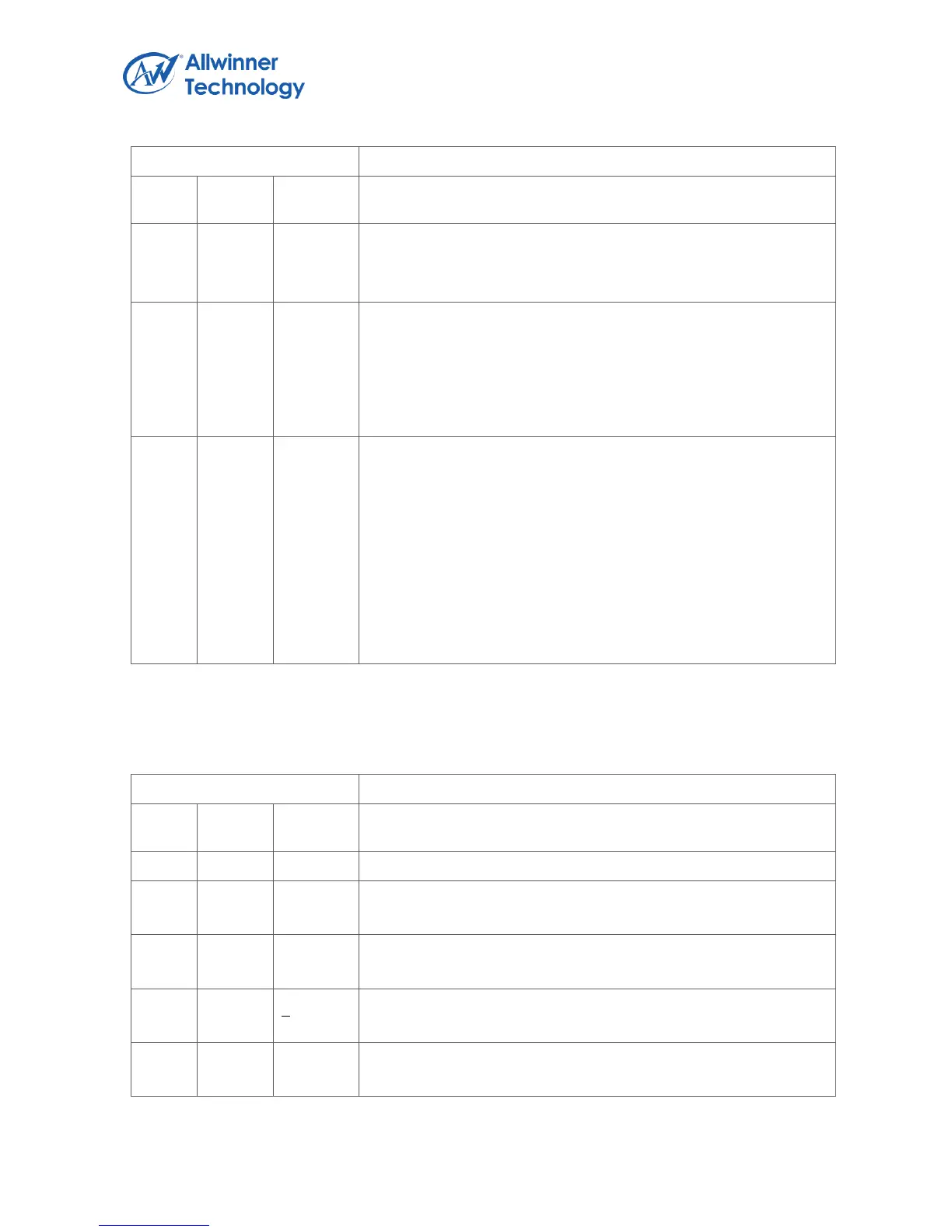

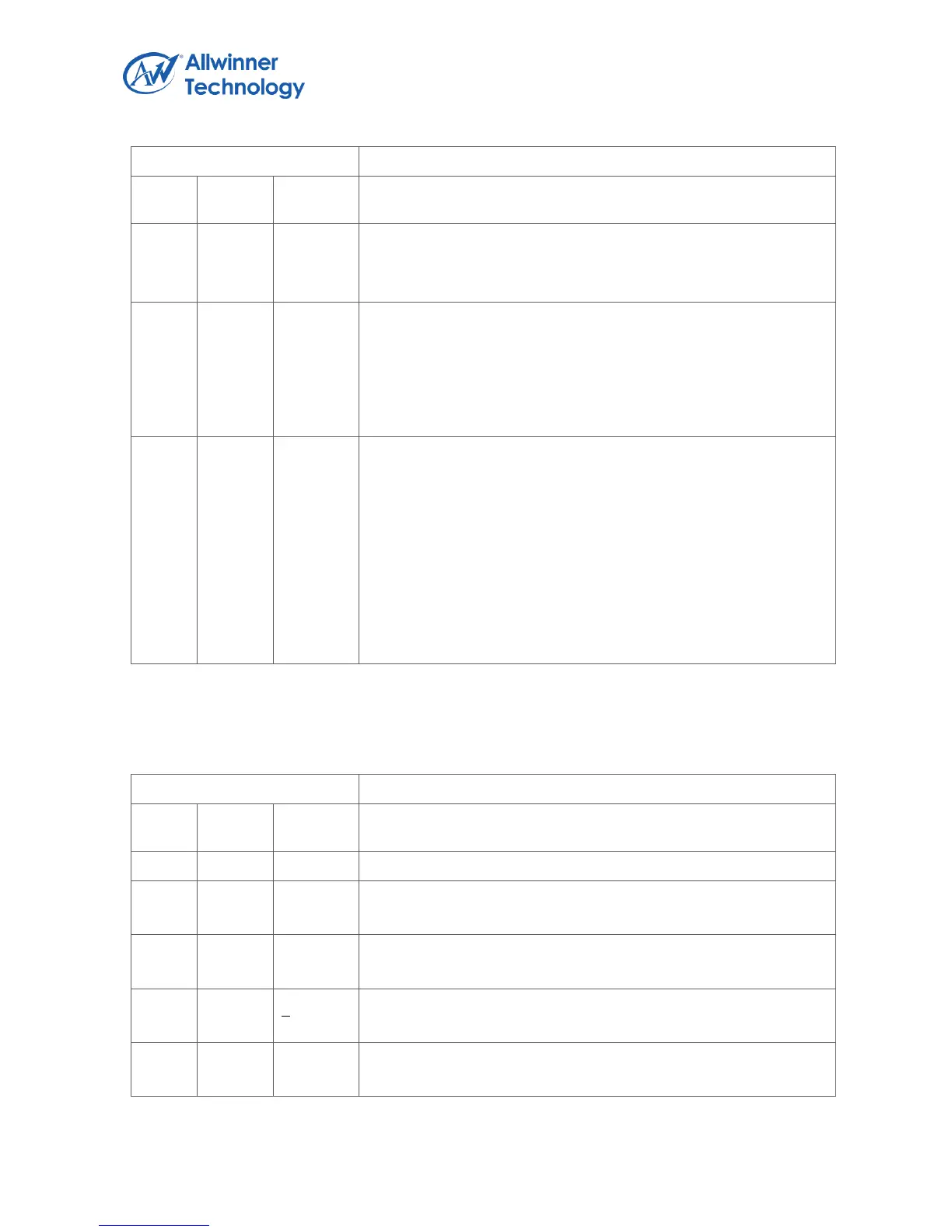

FD_INT_EN

Frame done

Indicates the CSI has finished capturing an image frame. Applies

to video capture mode. The bit is set after each completed frame

capturing data is wrote to buffer as long as video capture

remains enabled.

CD_INT_EN

Capture done

Indicates the CSI has completed capturing the image data.

For still capture, the bit is set when one frame data has been

wrote to buffer.

For video capture, the bit is set when the last frame has been

wrote to buffer after video capture has been disabled.

For CCIR656 interface, if the output format is frame planar

YCbCr 420 mode, the frame end means the field2 end, the other

frame end means field end.

Loading...

Loading...