A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 413 / 812

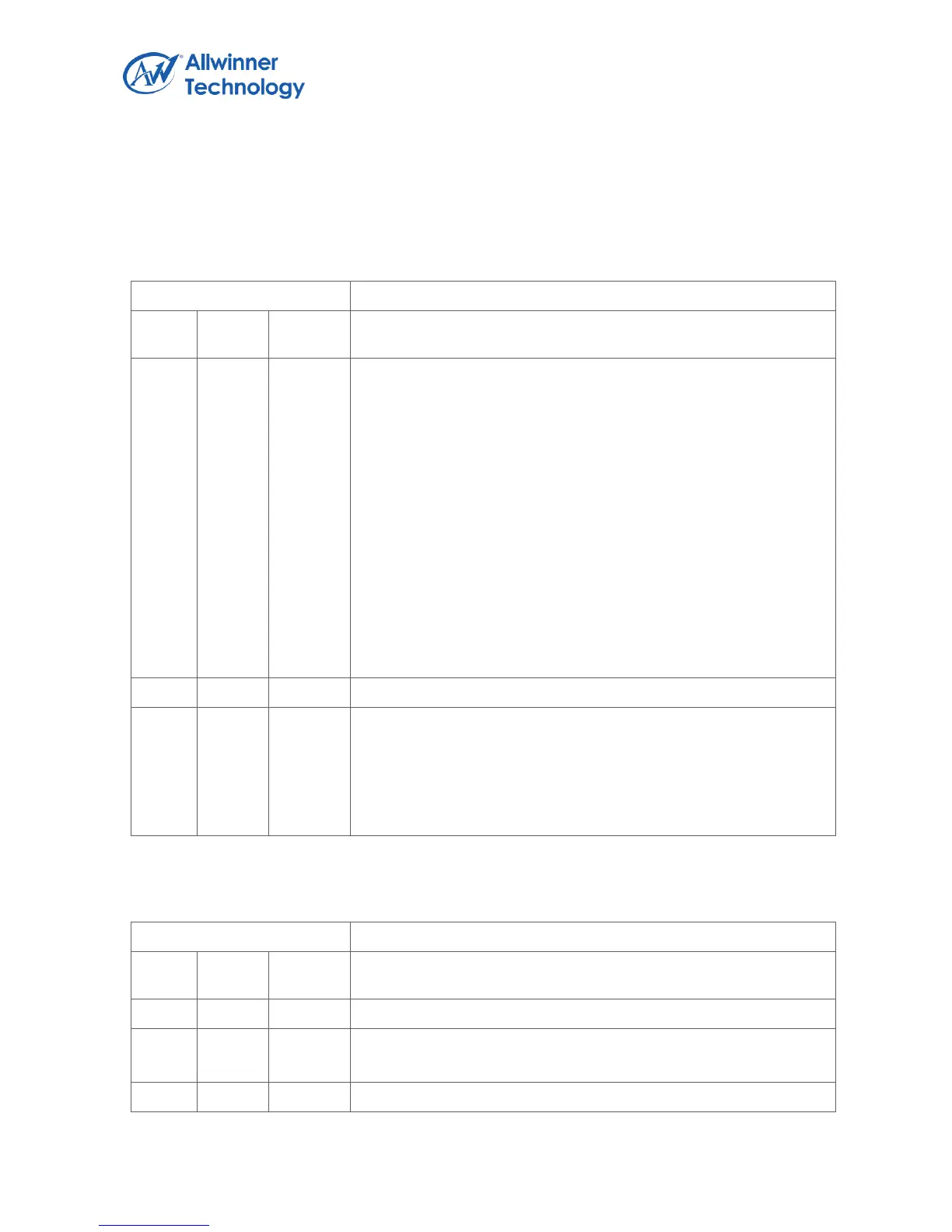

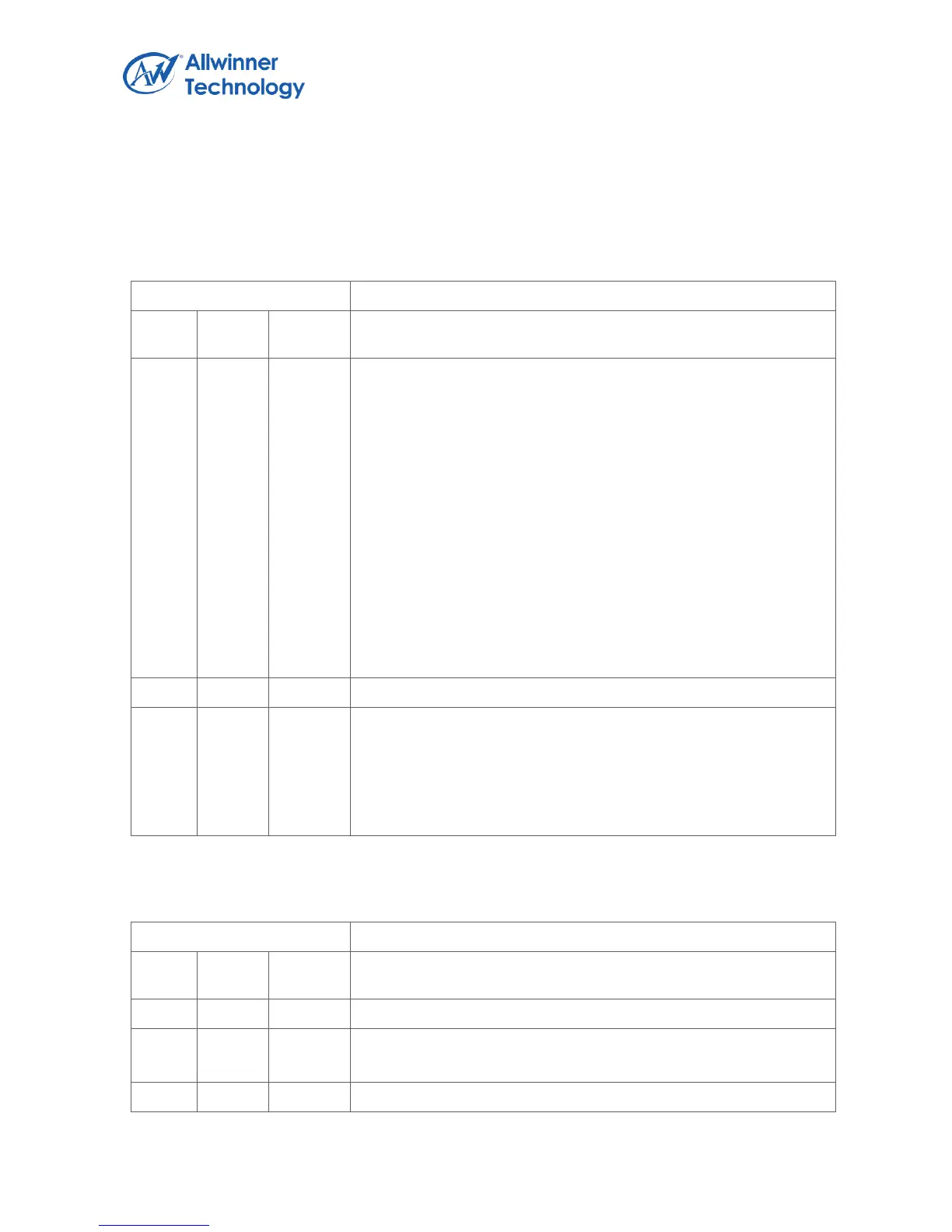

5.1.4.5. TCON0 DATA CLOCK REGISTER

TCON0_Dclk_En

LCLK_EN[3:0] :TCON0 clock enable

4’h0,

‘h4,4’h6,4’ha7:dclk_en=0;dclk1_en=0;dclk2_en=0;dclkm2_en=0;

4’h1: dclk_en = 1; dclk1_en = 0; dclk2_en = 0; dclkm2_en = 0;

4’h2: dclk_en = 1; dclk1_en = 0; dclk2_en = 0; dclkm2_en = 1;

4’h3: dclk_en = 1; dclk1_en = 1; dclk2_en = 0; dclkm2_en = 0;

4’h5: dclk_en = 1; dclk1_en = 0; dclk2_en = 1; dclkm2_en = 0;

4’h8,4’h9,4’ha,4’hb,4’hc,4’hd,4’he,4’hf:

dclk_en = 1;

dclk1_en = 1;

dclk2_en = 1;

dclkm2_en = 1;

TCON0_Dclk_Div

Tdclk = Tsclk * DCLKDIV

Note:

1.if dclk1&dclk2 used,DCLKDIV >=6

2.if dclk only,DCLKDIV >=4

Loading...

Loading...