A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 417 / 812

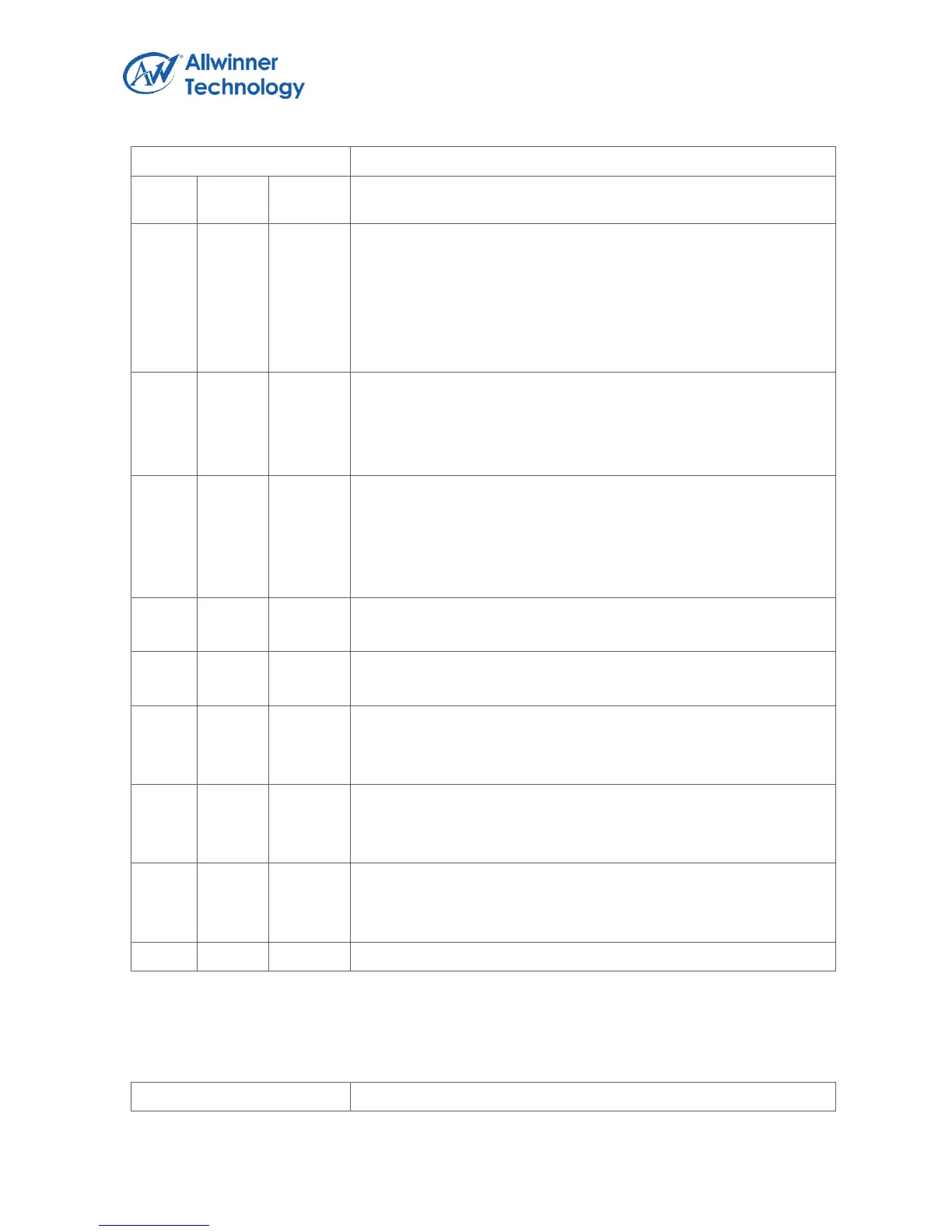

Register Name: TCON0_CPU_IF_REG

010: 16bit mode1

011: 16bit mode2

100: 16bit mode3

101: 9bit mode

110: 8bit 256K mode

111: 8bit 65K mode

AUTO

auto Transfer Mode:

If it’s 1, all the valid data during this frame are write to panel.

Note: This bit is sampled by Vsync

FLUSH

direct transfer mode:

If it’s enabled, FIFO1 is regardless of the HV timing, pixels data

keep being transferred unless the input FIFO was empty.

Data output rate control by DCLK.

DA

pin A1 value in 8080 mode auto/flash states

CA

pin A1 value in 8080 mode WR/RD execute

VSYNC_Cs_Sel

0:CS

1:VSYNC

Wr_Flag

0:write operation is finishing

1:write operation is pending

Rd_Flag

0:read operation is finishing

1:read operation is pending

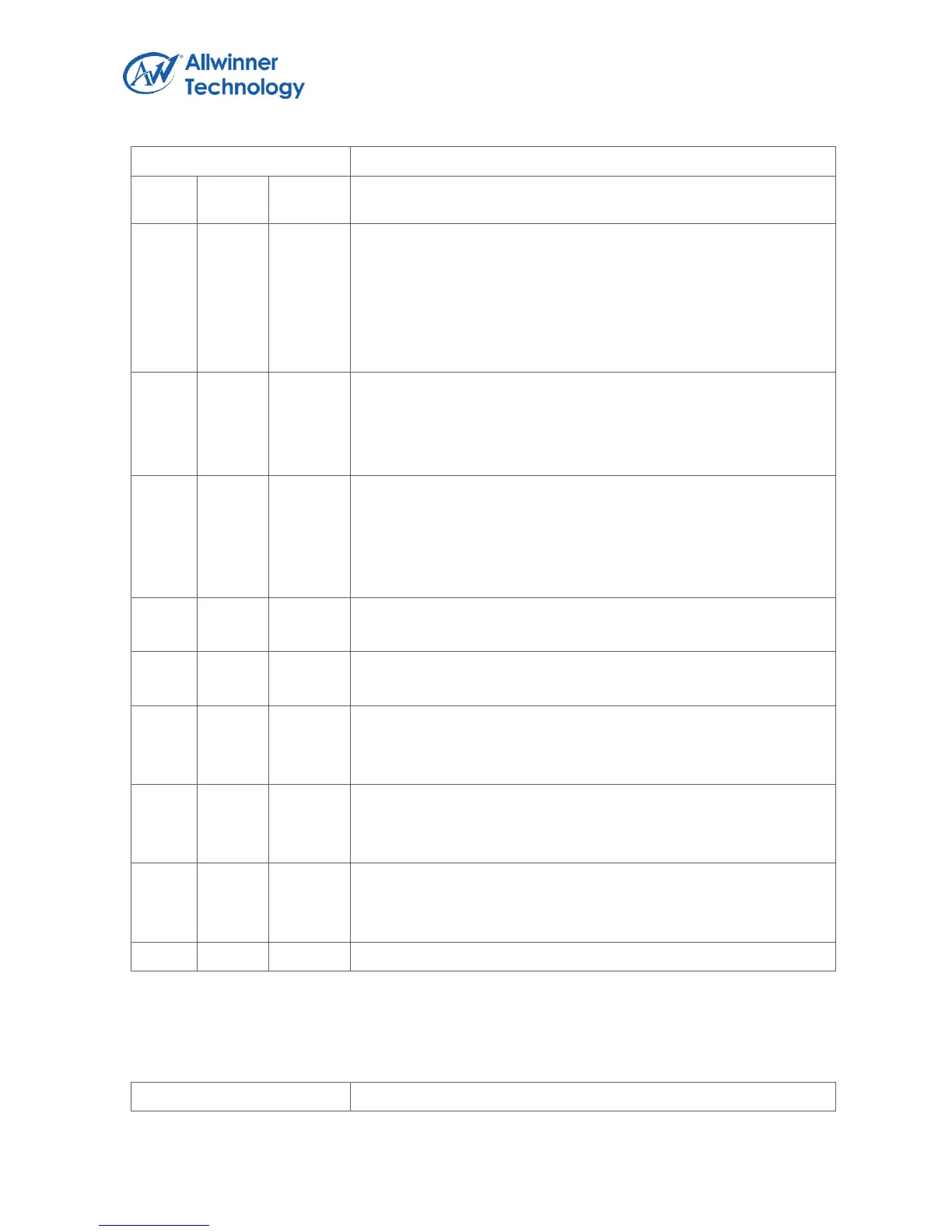

5.1.4.12. TCON0 CPU PANEL WRITE DATA REGISTER

Register Name: TCON0_CPU_WR_REG

Loading...

Loading...