A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 418 / 812

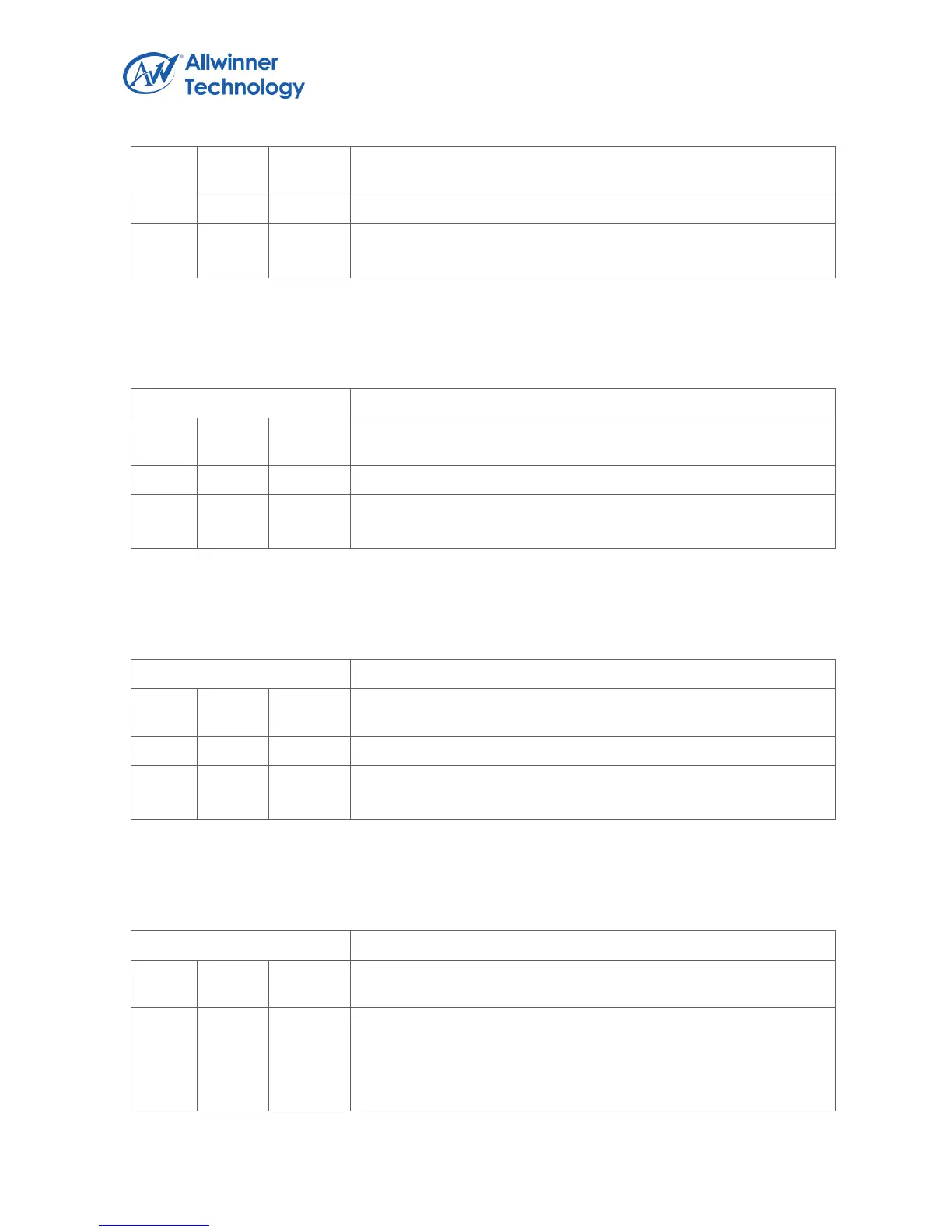

Data_Wr

data write on 8080 bus, launch a write operation on 8080 bus

5.1.4.13. TCON0 CPU PANEL READ DATA REGISTER0

Register Name: TCON0_CPU_RD0_REG

Data_Rd0

data read on 8080 bus, launch a new read operation on 8080 bus

5.1.4.14. TCON0 CPU PANEL READ DATA REGISTER1

Register Name: TCON0_CPU_RD1_REG

Data_Rd1

data read on 8080 bus, without a new read operation on 8080 bus

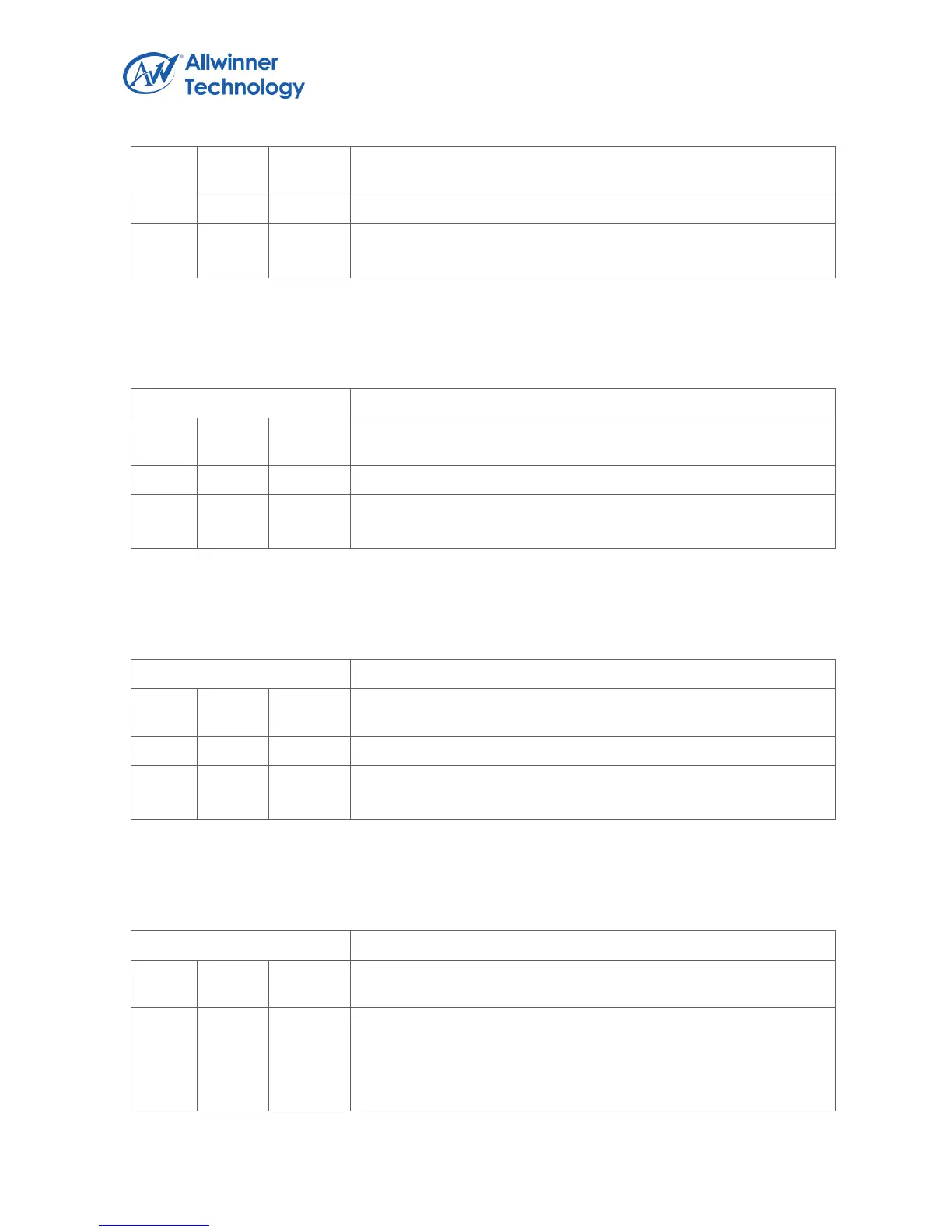

5.1.4.15. TCON0 TTL PANEL TIMING REGISTER 0

Register Name: TCON0_TTL0_REG

STVH

STV high plus width (in dclk)

Tstvh = (STVH +1) * Tdclk

Note: STV has a period of one frame

Loading...

Loading...