A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 421 / 812

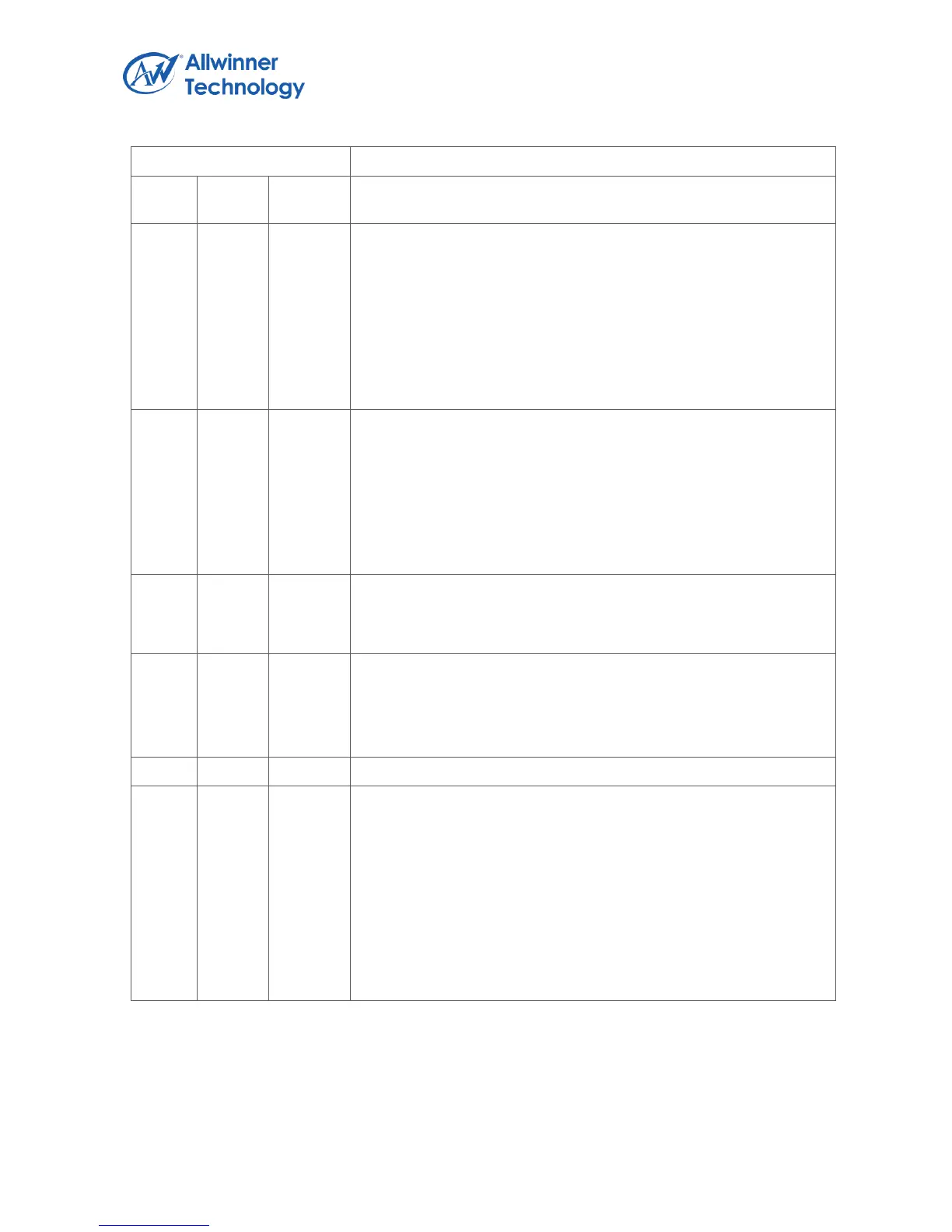

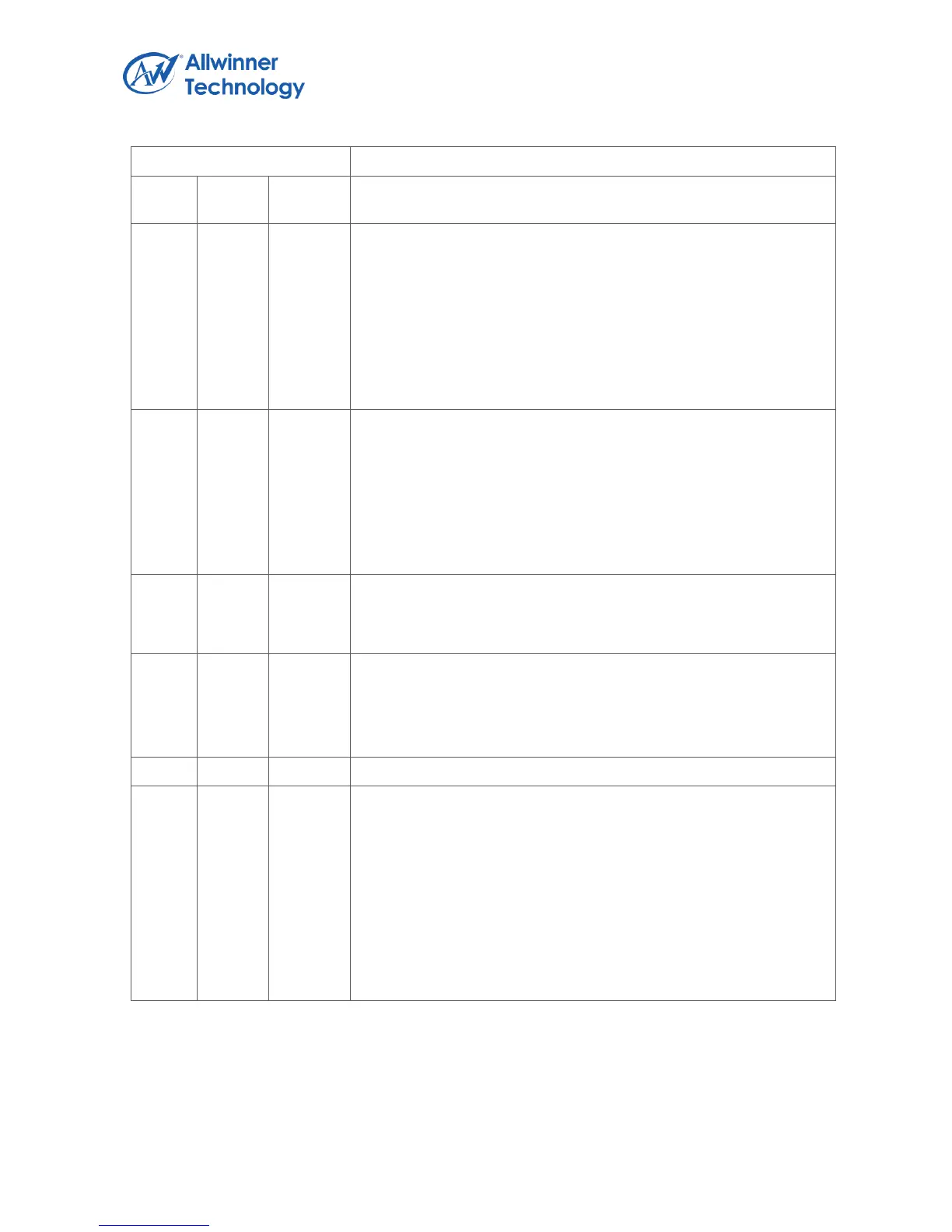

Register Name: TCON0_TTL4_REG

0: single data rate (SDR).

LCD read data at the rising edge of clock

1: Double data rate (DDR).

(The first data of every line must be ready at rising edge of

CKH/CKH1/CKH2.)

Note: When DATA_RATE = 1, HT and HBP had better be even

number;

CKH-CKH1 and CKH1-CKH2 delay time is always 1/3 Tdclk

Rev_Sel

REV toggle mode

0:1H time toggle mode with frame inversion

1: Frame toggle mode

Note: no matter in which mode, make sure REV has different

polarity at the beginning of every frame (take VSYNC as

reference).

TTL_Data_Inv_En

0: disable

1: data inverted ref to REV signal

TTL_Data_Inv_Sel

TTL data invert mode

0: bit inverted when REV is 1

1: bit inverted when REV is 0

REVD

HSYNC-REV delay time(in dclk)

T

revd

= REVD * T

dclk

Note:

1. When

REV_SEL

is 0, REV has a 2H period with 50% duty.

2. When

REV_SEL

is 1, REV has a 2 Frame period with 50%

duty.

3. Make sure REV has different polarity at the beginning of every

frame(take VSYNC as reference).

Loading...

Loading...