A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 472 / 812

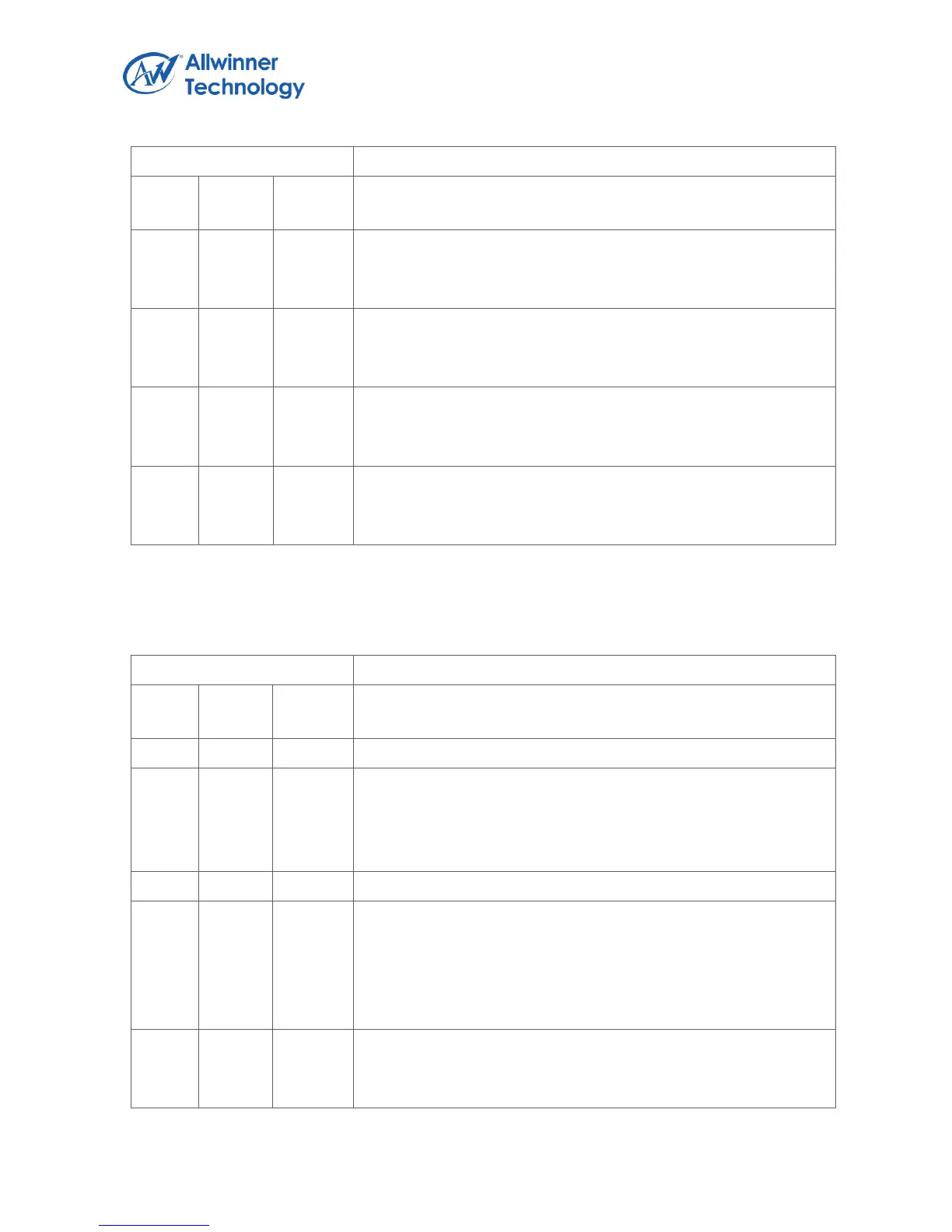

Register name: DDC_Int_Mask

DDC_Arbitration_Error_Int_Mask

0: disable

1: enable

DDC_ACK_Error_Int_Mask

0: disable

1: enable

DDC_Bus_Error_Int_Mask

0: disable

1: enable

DDC_Transfer_Complete_Int_Mask

0: disable

1: enable

5.2.4.36. DDC INTERRUPT STATUS REGISTER:

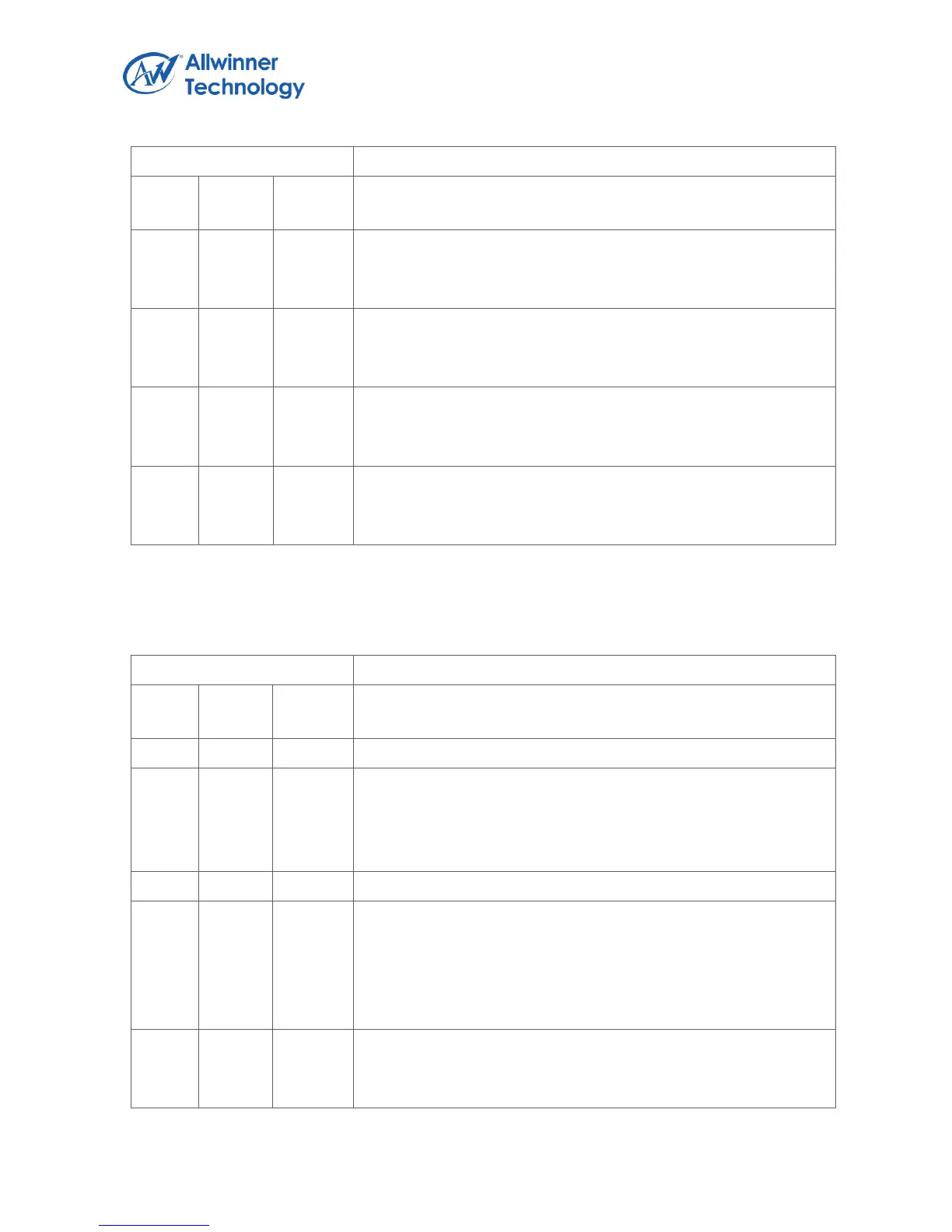

Register name: DDC_Int_Status

Interrupt_Clear_Status

0: Interrupt have be cleared

1: Interrupt clear is in process

Note : When clear interrupt, must check this bit for clear complete

Illegal_FIFO_operation_interrupt_status_bit

DDC_RX FIFO_Underflow_Interrupt_Status_Bit

0: not underflow

1: underflow

This bit is set when FIFO underflow

Write 1 to this bit will clear it

DDC_TX FIFO_Overflow_Interrupt_Status_Bit

0: not overflow

1: overflow

Loading...

Loading...