A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 473 / 812

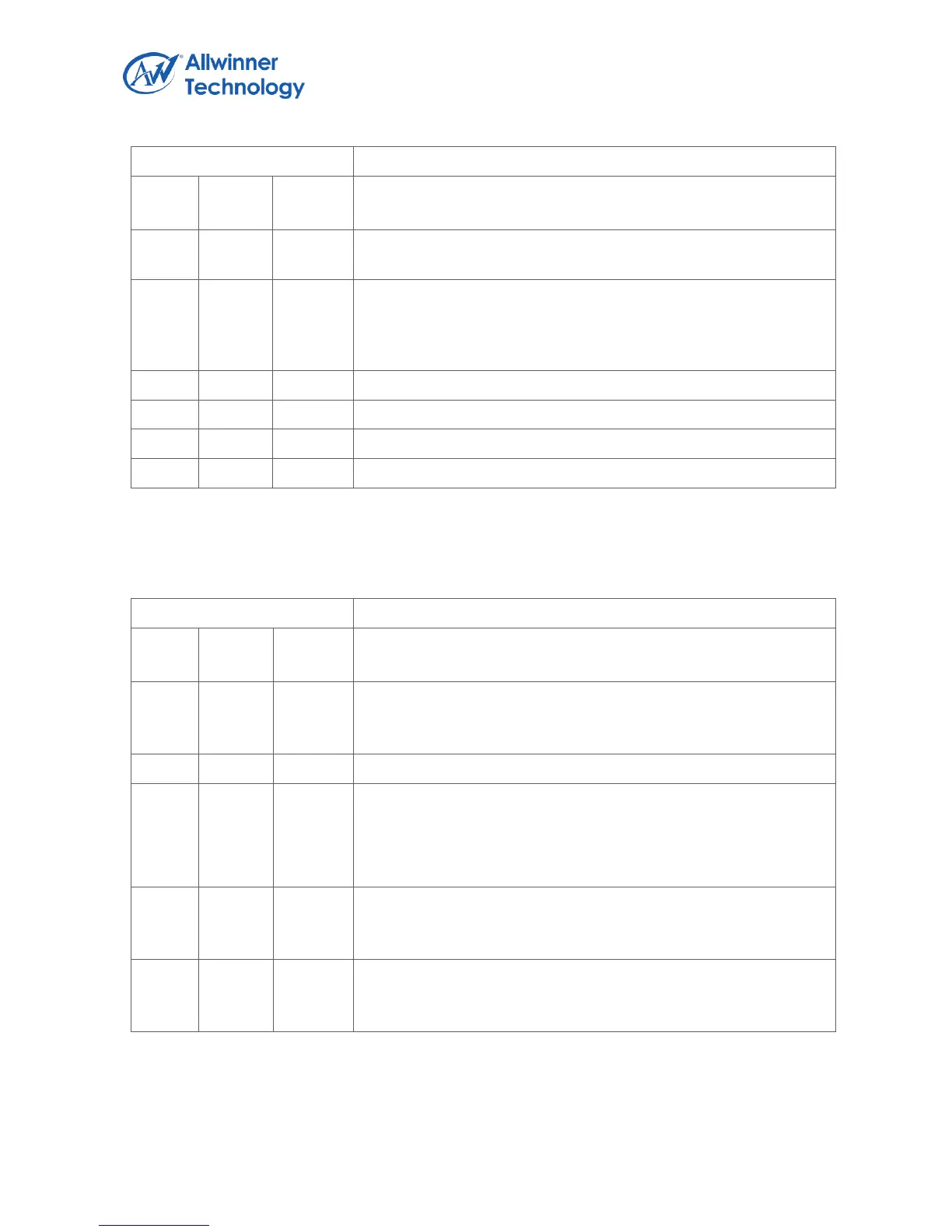

Register name: DDC_Int_Status

This bit is set when FIFO overflow

Write 1 to this bit will clear it

DDC_FIFO_Request_Interrupt_Status_Bit

This bit is set when TX FIFO level is below the TX trigger thresh in

write operation, or when RX FIFO level is above the RX trigger

thresh in read operation, write 1 to this bit will clear it.

DDC_ Arbitration_Error_Interrupt_Status_Bit

DDC_ACK_Error_Interrupt_Status_Bit

DDC_Bus_Error_Interrupt_Status_Bit

DDC_Transfer_Complete_Interrupt_Status_Bit

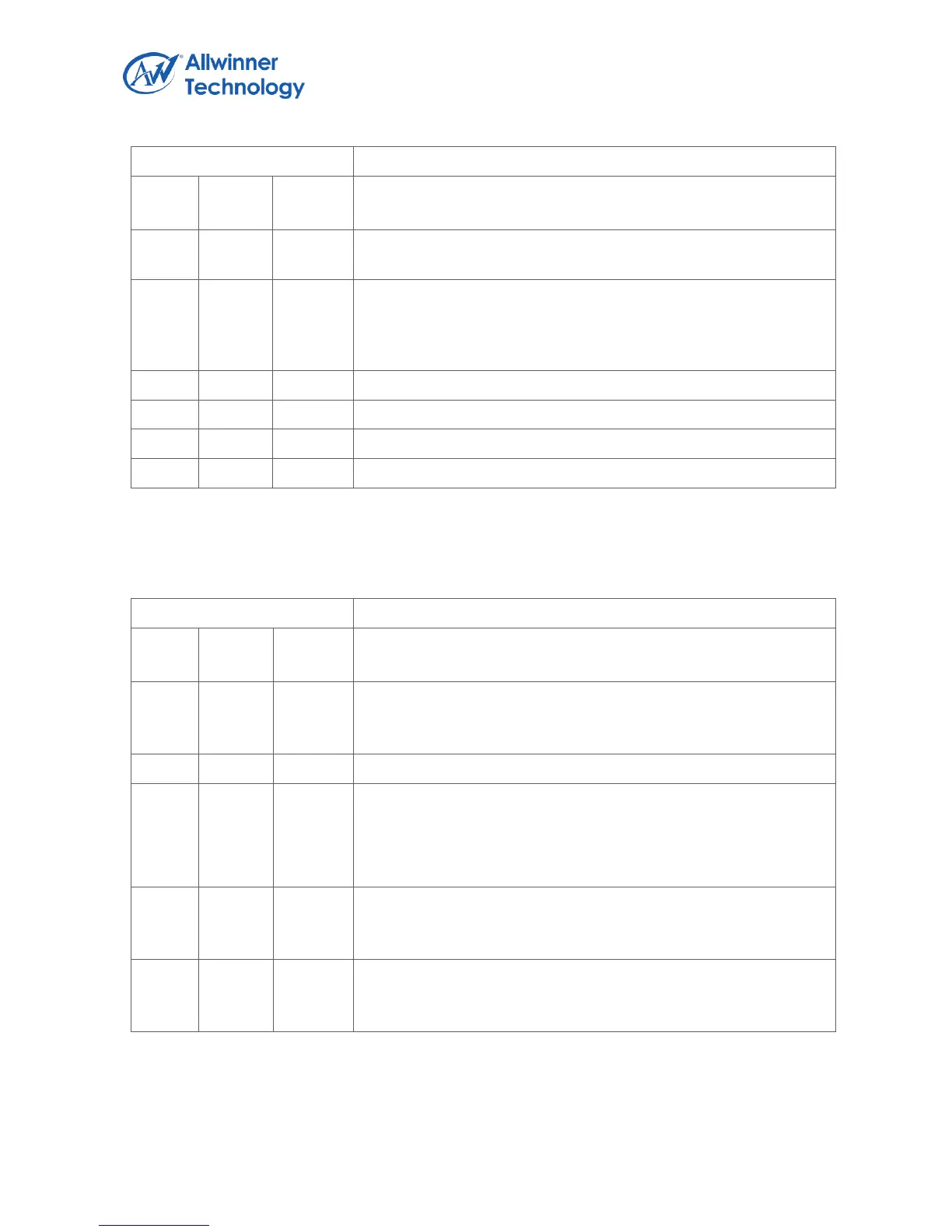

5.2.4.37. DDC FIFO CONTROL REGISTER

Register name: DDC_FIFO _Ctrl

FIFO_Address_Clear

Write ‘1’ to this bit will clear FIFO address, and auto clear to 0

when completing FIFO addresses clear operation.

DMA_Request_En

0: disable

1: enable

Note: this bit can only be set when correct FIFO direction is set

FIFO_RX_TRIGGER_THRESH

When FIFO level is above this value in read mode, DMA request

and FIFO request interrupt is assert if relative enable is on.

FIFO_TX_TRIGGER_THRESH

When FIFO level is below this value in write mode, DMA request

and FIFO request interrupt is assert if relative enable is on.

Loading...

Loading...