A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 475 / 812

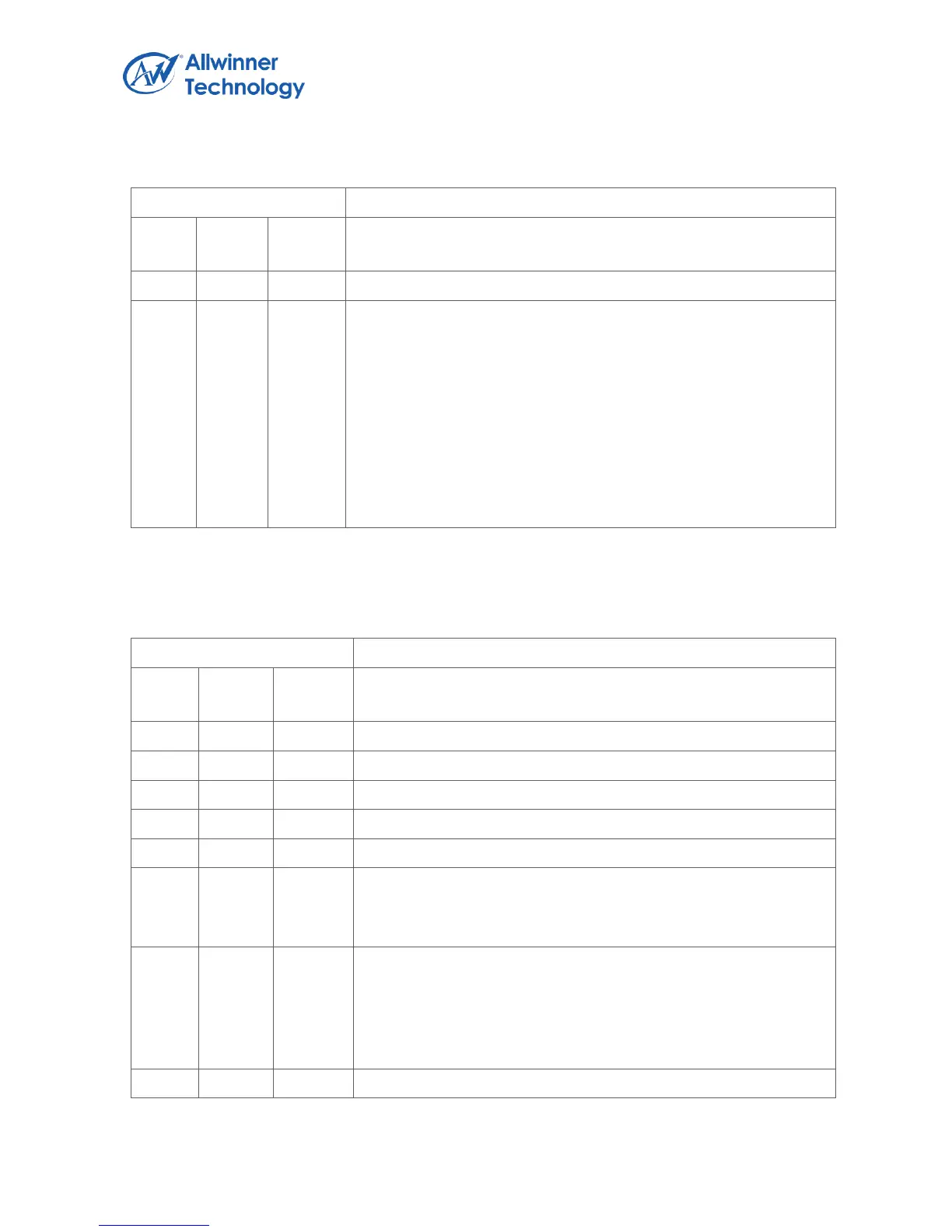

5.2.4.41. DDC ACCESS COMMAND REGISTER

Register name: DDC_Command

DDC_Access_Command

000 = Abort Current Operation

001 = Special Offset Address Read

010 = Explicit Offset Address Write

011 = Implicit Offset Address Write

100 =Explicit Offset Address Read

101 =Implicit Offset Address Read

110 = Explicit Offset Address E-DDC Read

111 = Implicit Offset Address E-DDC Read

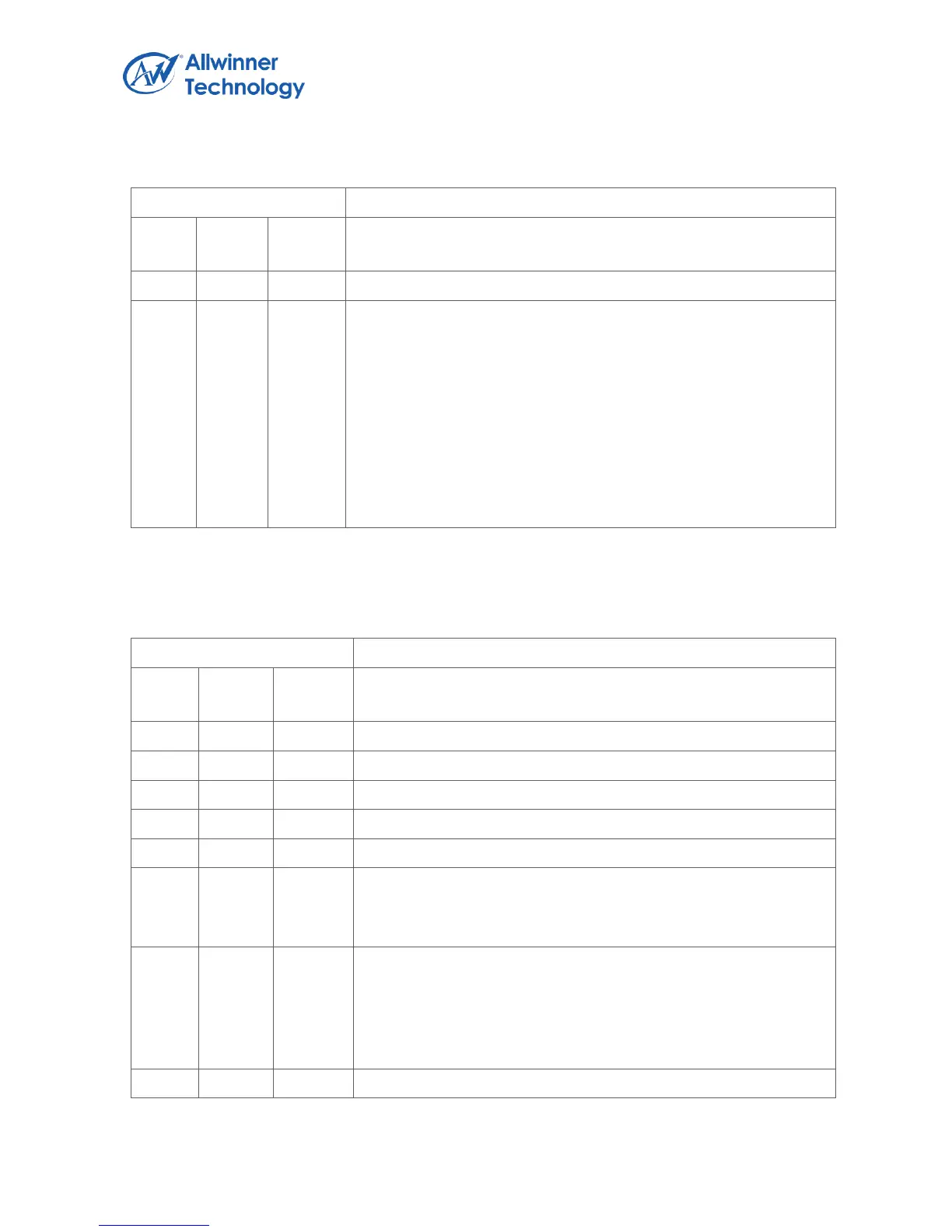

5.2.4.42. DDC EXTENDED REGISTER

DDC_SCL_LineState_Control_En

0: disable

1: enable

DDC_SCL_LineState_Control_Bit

When DDC_SCL line state control enable is set to ‘1’, the value of

this bit decide the output level of DDC_SCL

0: output low level

1: output high level

DDC_SDA _LineState_Control_Bit

Loading...

Loading...