A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 495 / 812

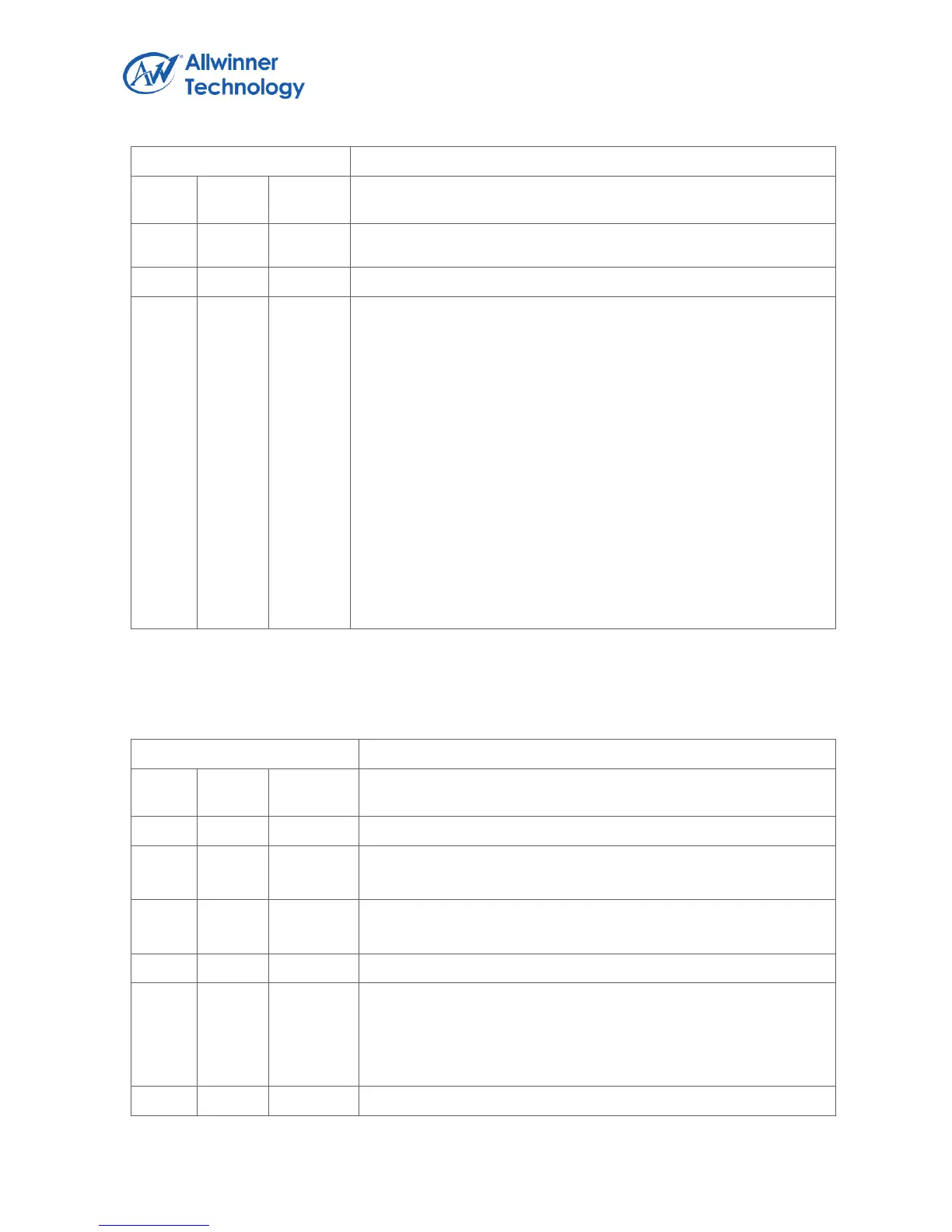

Register Name: DEFE_OUTPUT_FMT_REG

When output interlace enable, scaler selects YUV initial phase

according to LCD field signal

DATA_FMT

Data format

000: planar RGB888 conversion data format

001: interleaved BGRA8888 conversion data format(A component

always be pad 0xff)

010: interleaved ARGB8888 conversion data format(A component

always be pad 0xff)

100: planar YUV 444

101: planar YUV 420(only support YUV input and not interleaved

mode)

110: planar YUV 422(only support YUV input)

111: planar YUV 411(only support YUV input)

Other: reserved

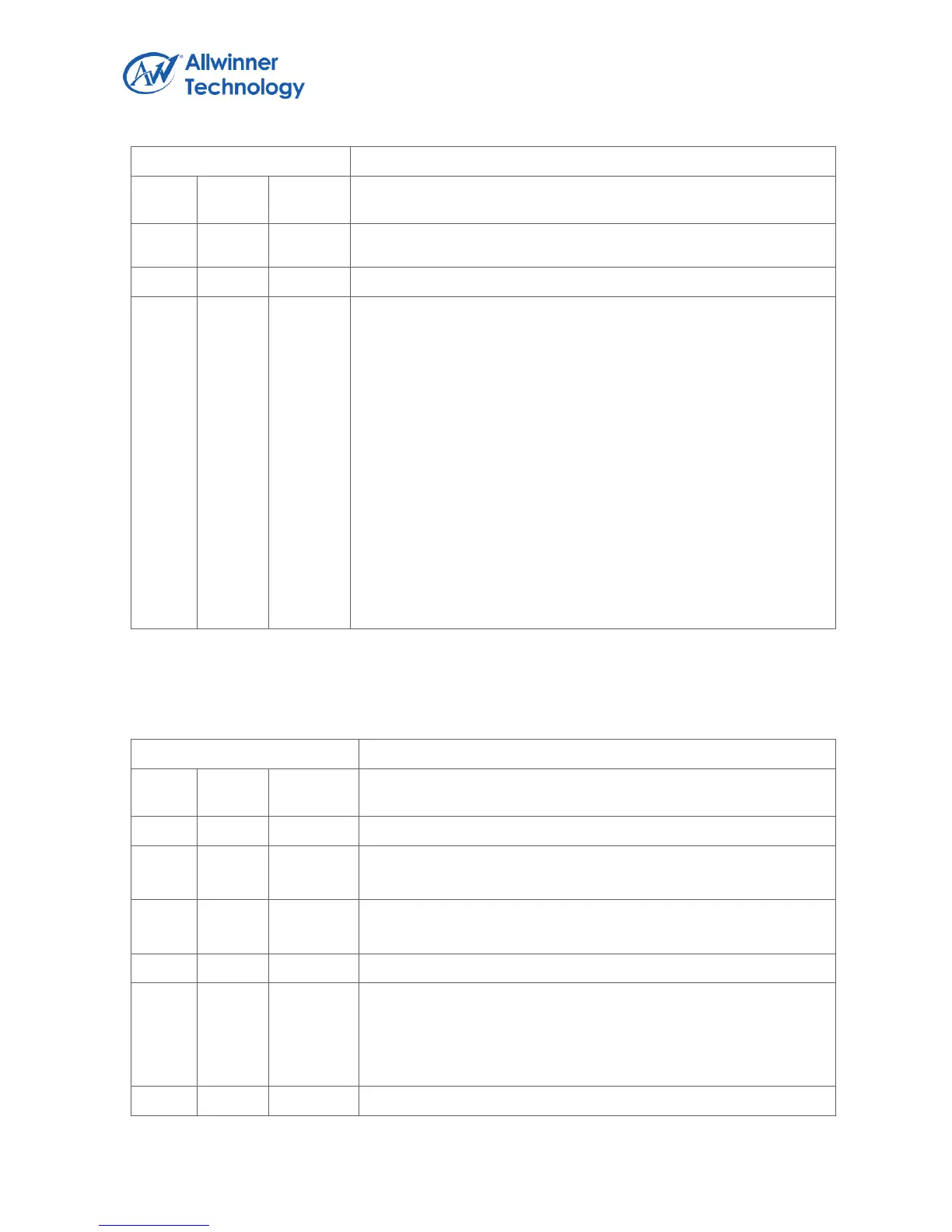

5.3.4.21. DEFE_INT_EN_REG

Register Name: DEFE_INT_EN_REG

REG_LOAD_EN

Register ready load interrupt enable

LINE_EN

Line interrupt enable

WB_EN

Write-back end interrupt enable

0: Disable

1: Enable

Loading...

Loading...