A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 50 / 812

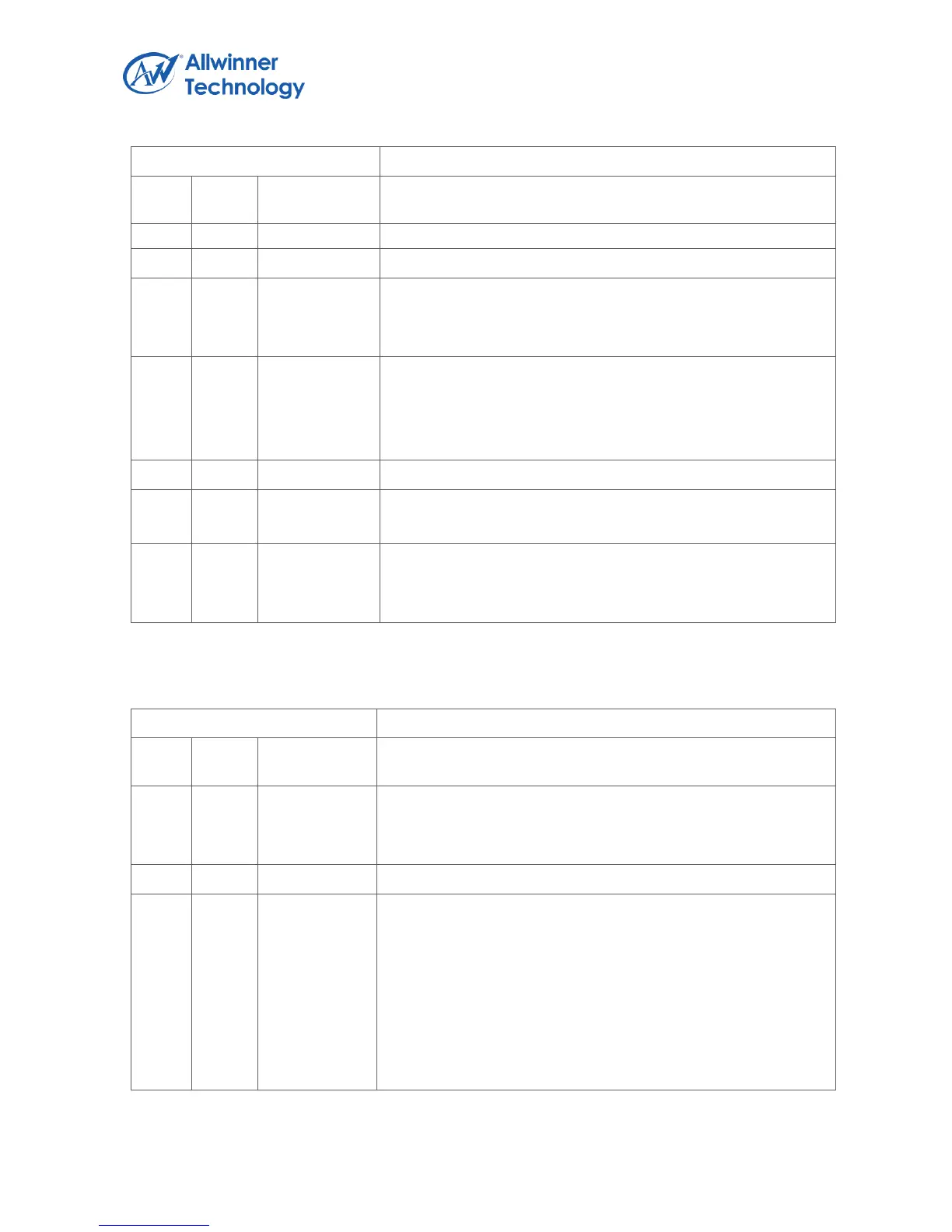

Register Name: OSC24M_CFG_REG

If the key field value is 0xA7, the bit[23:16] can be modified.

LDO_EN.

LDO Enable.

0: Disable, 1: Enable.

PLL_BIAS_EN.

PLL Bias Enable.

0: disable,

1: enable.

OSC24M_EN.

OSC24M Enable.

0: Disable, 1: Enable.

1.5.4.16. CPU/AHB/APB0 CLOCK RATIO(DEFAULT: 0X00010010)

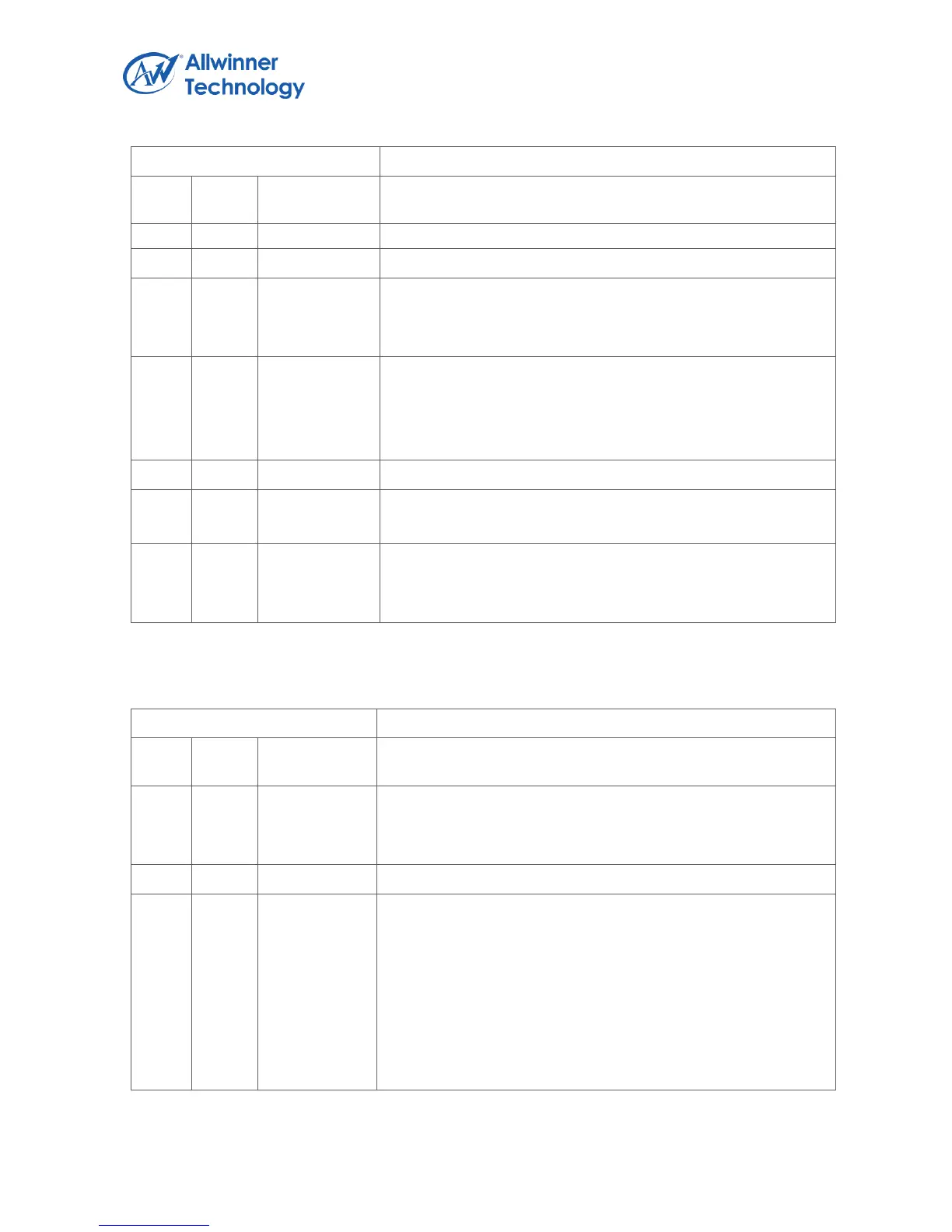

Register Name: CPU_AHB_APB0_CFG_REG

DVFS_START.

DVFS start. Set 1 to this bit will start the DVFS.

It will be cleared automatically after the DVFS is finished.

CPU_CLK_SRC_SEL.

CPU0/1 Clock Source Select.

00: LOSC

01: OSC24M

10: PLL1

11: 200MHz(source from the PLL6).

If the clock source is changed, at most to wait for 8 present

running clock cycles.

Loading...

Loading...