A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 52 / 812

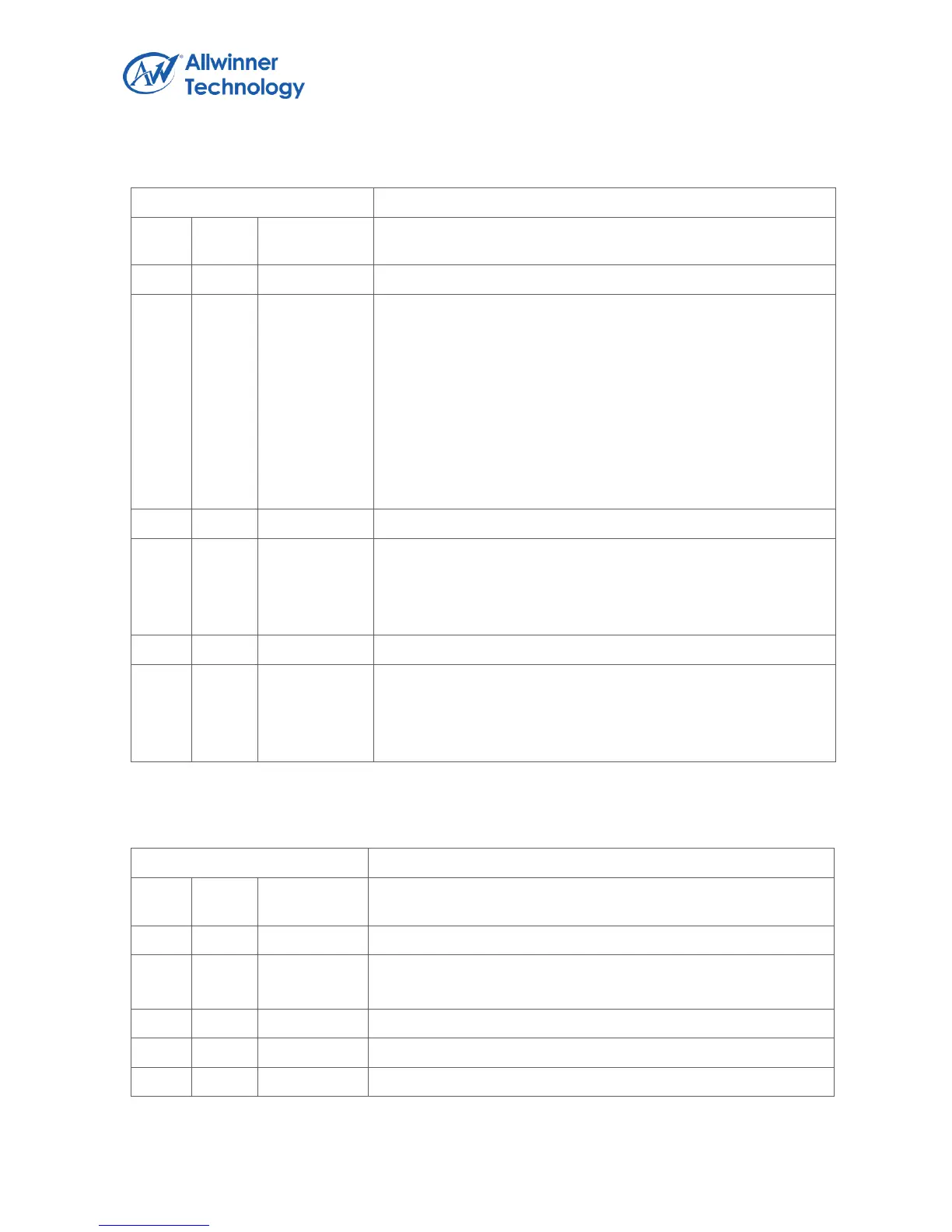

1.5.4.17. APB1 CLOCK DIVIDE RATIO(DEFAULT: 0X00000000)

Register Name: APB1_CLK_DIV_REG

APB1_CLK_SRC_SEL.

APB1 Clock Source Select

00: OSC24M

01: PLL6

10: LOSC

11: /

This clock is used for some special module apbclk(twi,uart,

ps2, can, scr). Because these modules need special clock rate

even if the apbclk changed.

CLK_RAT_N

Clock pre-divide ratio (n)

The select clock source is pre-divided by 2^n. The divider is

1/2/4/8.

CLK_RAT_M.

Clock divide ratio (m)

The pre-divided clock is divided by (m+1). The divider is from 1

to 32.

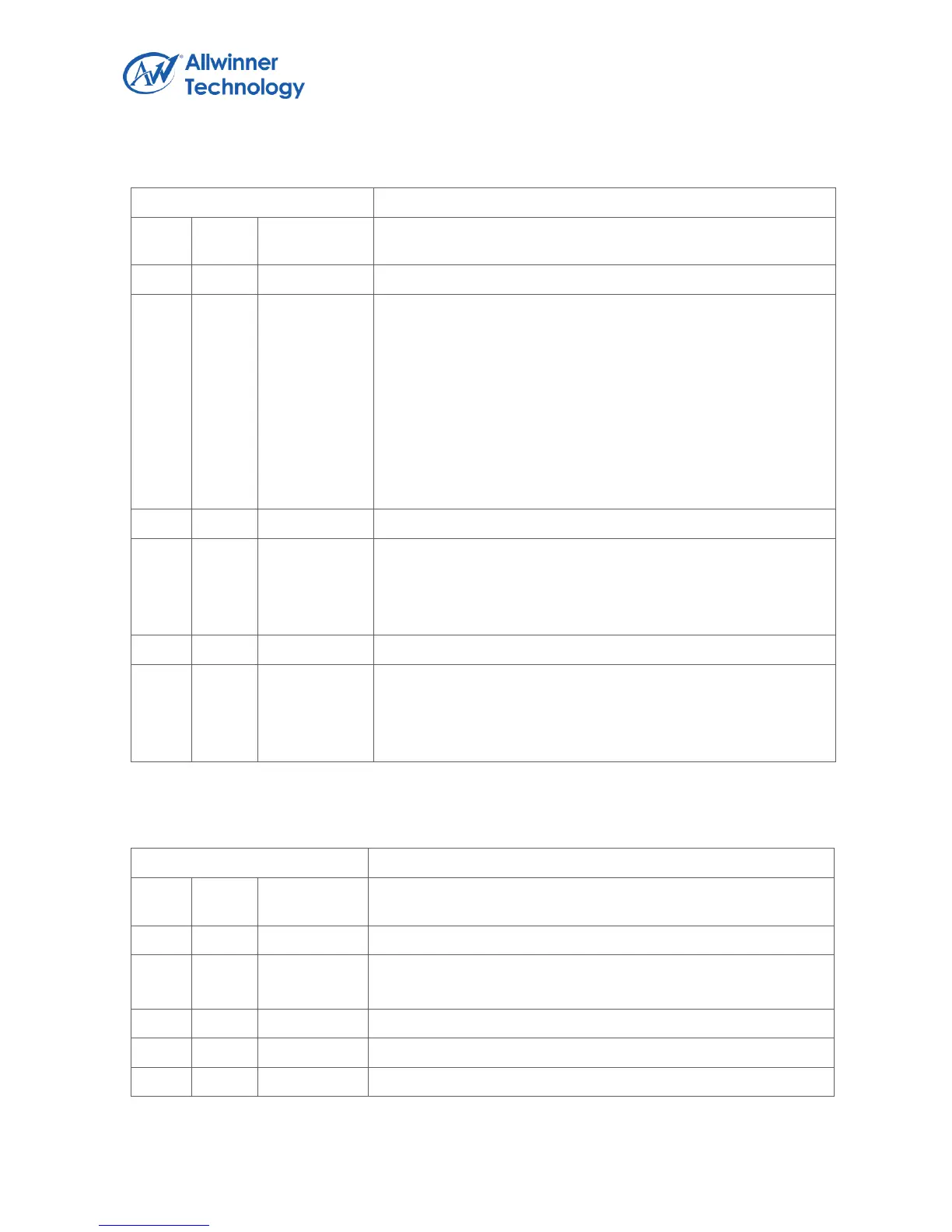

1.5.4.18. AHB MODULE CLOCK GATING REGISTER 0(DEFAULT: 0X00000000)

Register Name: AHB_GATING_REG0

STIMER_AHB_GATING

Gating AHB Clock for Sync timer(0:mask,1:pass)

Gating AHB Clock for SATA(0: mask, 1: pass).

Loading...

Loading...