A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 581 / 812

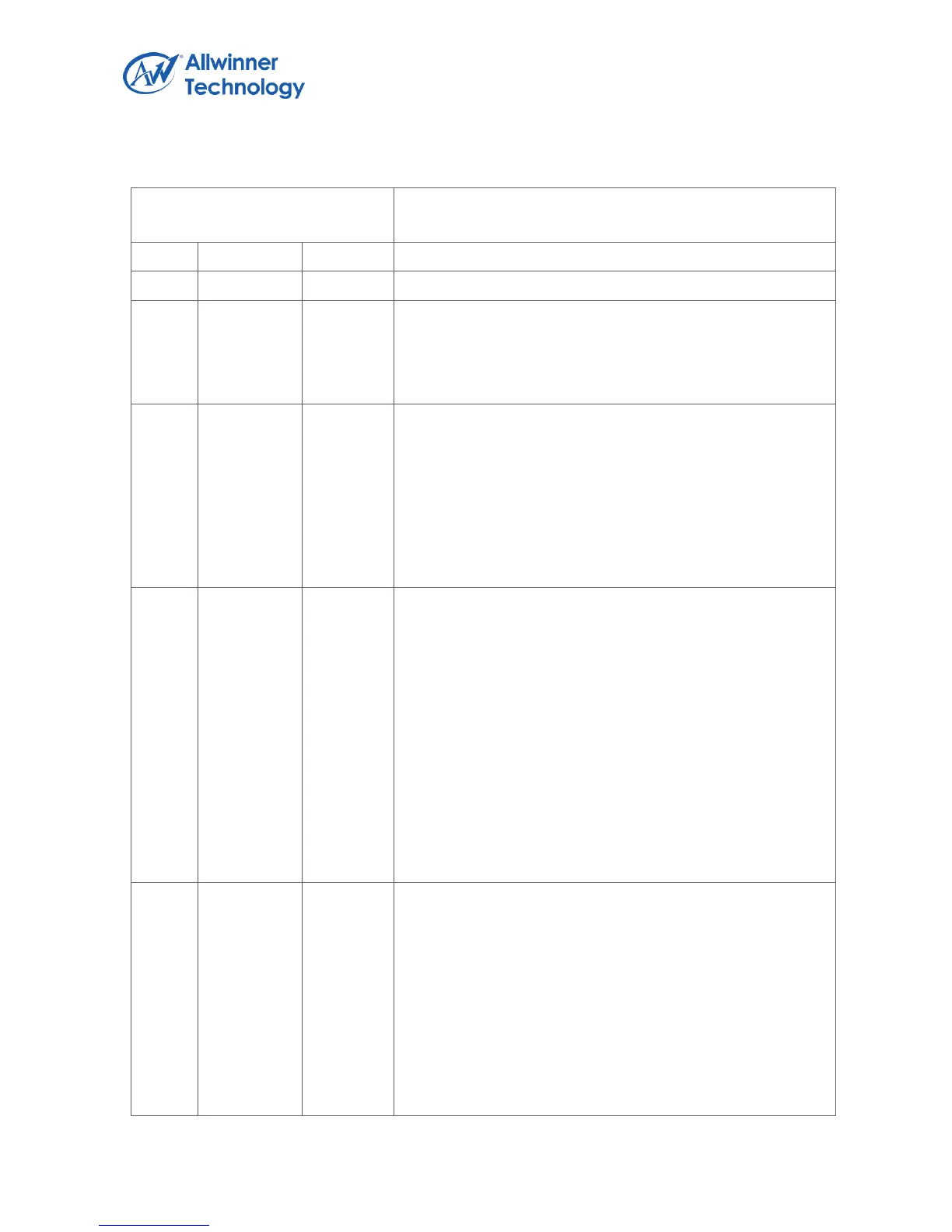

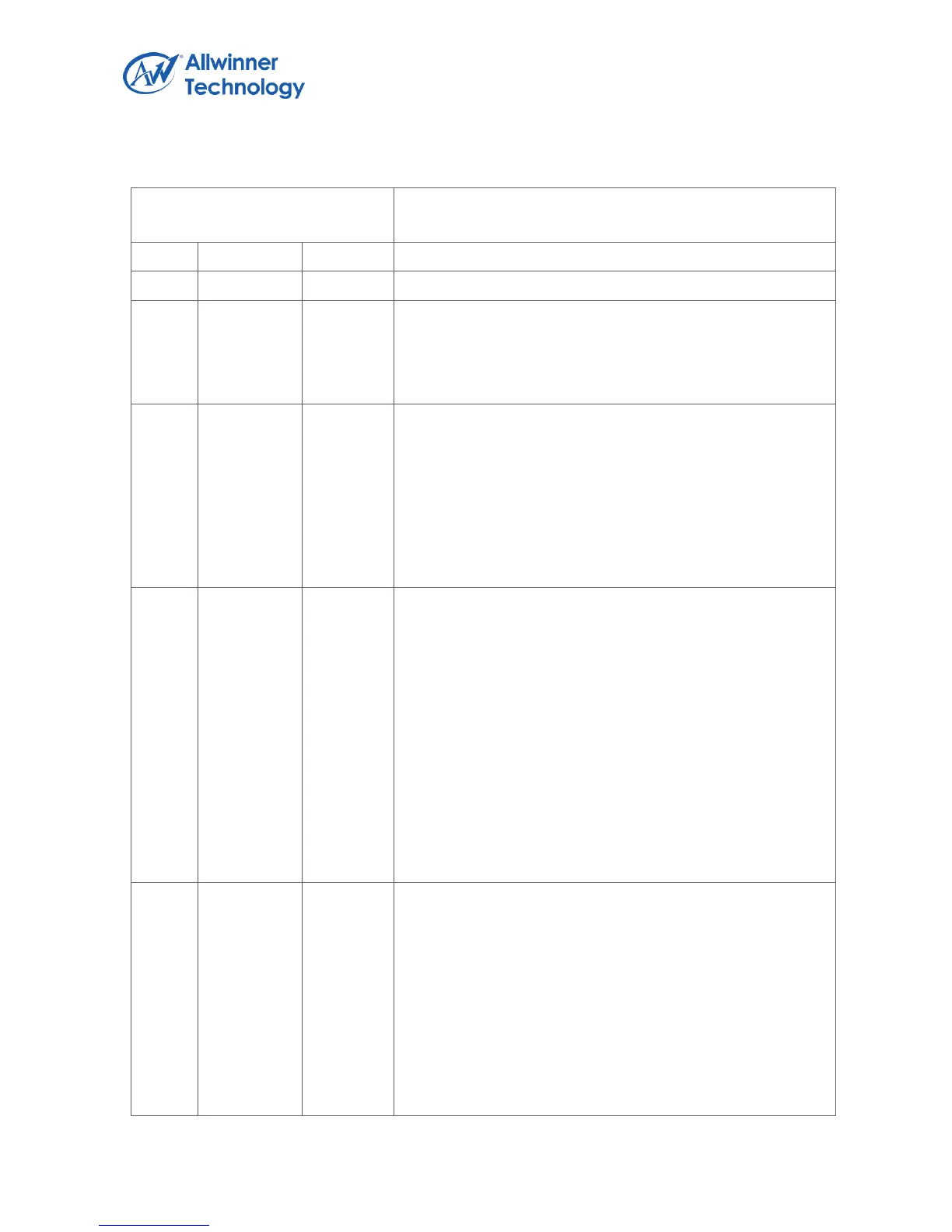

6.2.4.4. TWI CONTROL REGISTER

Register Name: TWI_CNTR

Default Value: 0x0000_0000

INT_EN

Interrupt Enable

1’b0: The interrupt line always low

1’b1: The interrupt line will go high when INT_FLAG is set.

BUS_EN

2-Wire Bus Enable

1’b0: The 2-Wire bus inputs ISDA/ISCL are ignored and the

2-Wire Controller will not respond to any address on the bus

1’b1: The TWI will respond to calls to its slave address –

and to the general call address if the GCE bit in the ADDR

register is set.

Notes: In master operation mode, this bit should be set to ‘1’

M_STA

Master Mode Start

When M_STA is set to ‘1’, TWI Controller enters master

mode and will transmit a START condition on the bus when

the bus is free. If the M_STA bit is set to ‘1’ when the 2-Wire

Controller is already in master mode and one or more bytes

have been transmitted, then a repeated START condition

will be sent. If the M_STA bit is set to ‘1’ when the TWI is

being accessed in slave mode, the TWI will complete the

data transfer in slave mode then enter master mode when

the bus has been released.

The M_STA bit is cleared automatically after a START

condition has been sent: writing a ‘0’ to this bit has no effect.

M_STP

Master Mode Stop

If M_STP is set to ‘1’ in master mode, a STOP condition is

transmitted on the 2-Wire bus. If the M_STP bit is set to ‘1’

in slave mode, the TWI will behave as if a STOP condition

has been received, but no STOP condition will be

transmitted on the 2-Wire bus. If both M_STA and M_STP

bits are set, the TWI will first transmit the STOP condition (if

in master mode) then transmit the START condition.

The M_STP bit is cleared automatically: writing a ‘0’ to this

Loading...

Loading...