A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 604 / 812

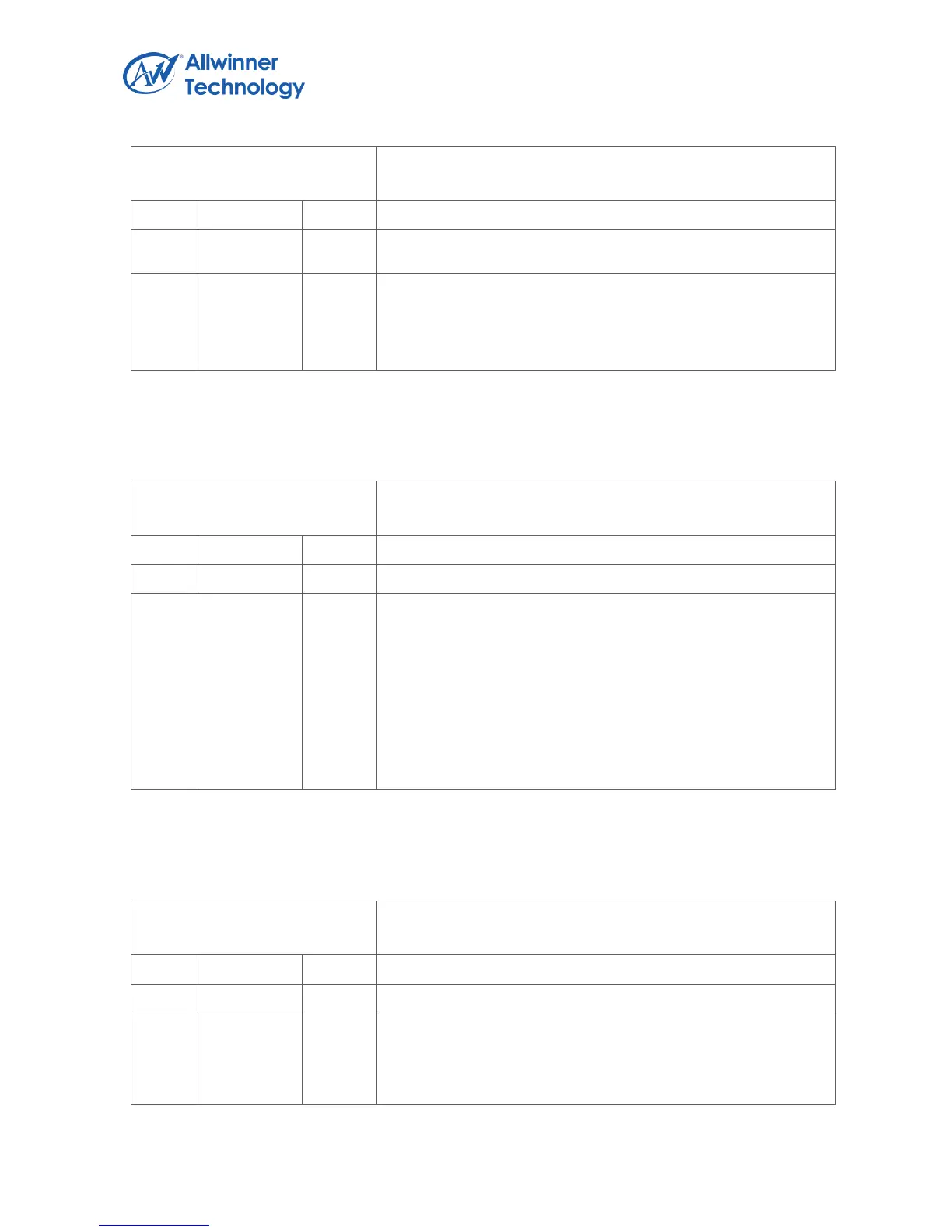

Register Name: SPI_CCTL

Default Value: 0x0000_0002

SPI_SCLK is determined according to the following equation:

SPI_CLK = AHB_CLK / 2^(n+1).

CDR2

Clock Divide Rate 2 (Master Mode Only)

The SPI_SCLK is determined according to the following

equation: SPI_CLK = AHB_CLK / (2*(n + 1)).

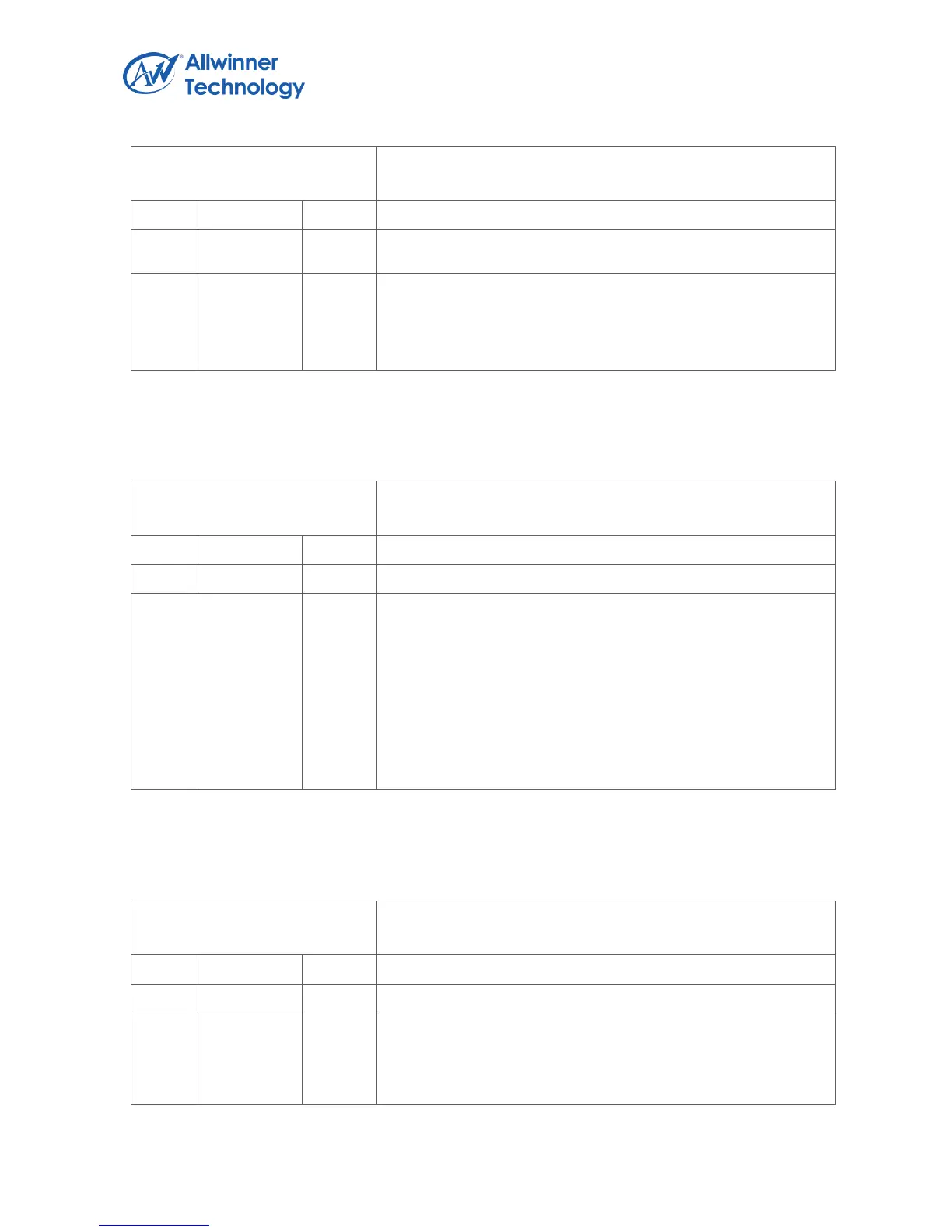

6.3.4.9. SPI BURST COUNTER REGISTER

Register Name: SPI_BC

Default Value: 0x0000_0000

BC

Burst Counter

In master mode, this field specifies the total burst number

when SMC is 1.

0: 0 burst

1: 1 burst

…

N: N bursts

6.3.4.10. SPI TRANSMIT COUNTER REGISTER

Register Name: SPI_TC

Default Value: 0x0000_0000

WTC

Write Transmit Counter

In master mode, this field specifies the burst number that

should be sent to TXFIFO before automatically sending

Loading...

Loading...