A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 635 / 812

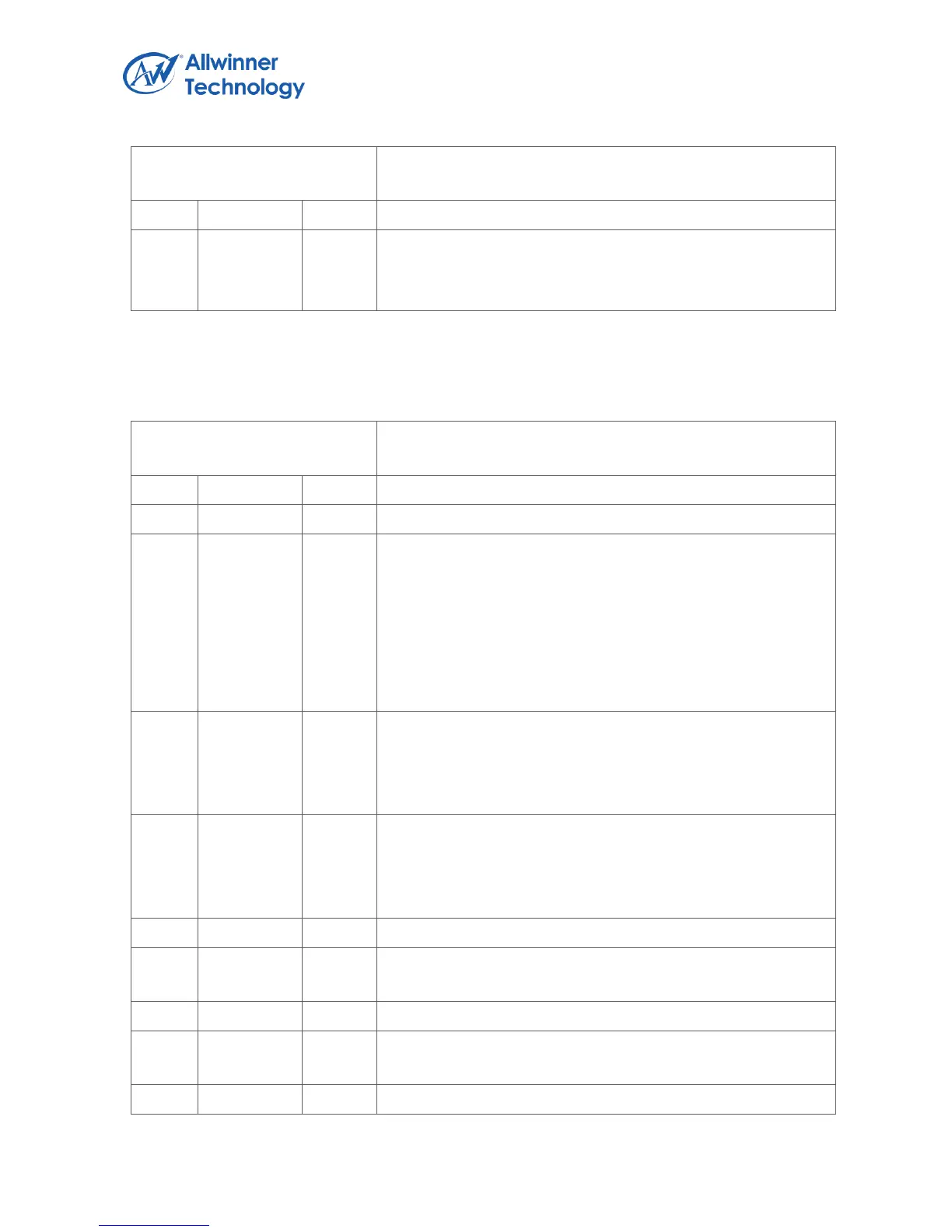

Register Name: PS2_DATA

Default Value: 0x0000_0000

Note: (1) After TXFIFO is full, writing does not affect anything

except the overflow flag of TXFIFO in FIFO Status Register.

(2) After RXFIFO is empty, reading has no effect on anything

except the underflow flag of RXFIFO in FIFO Status Register.

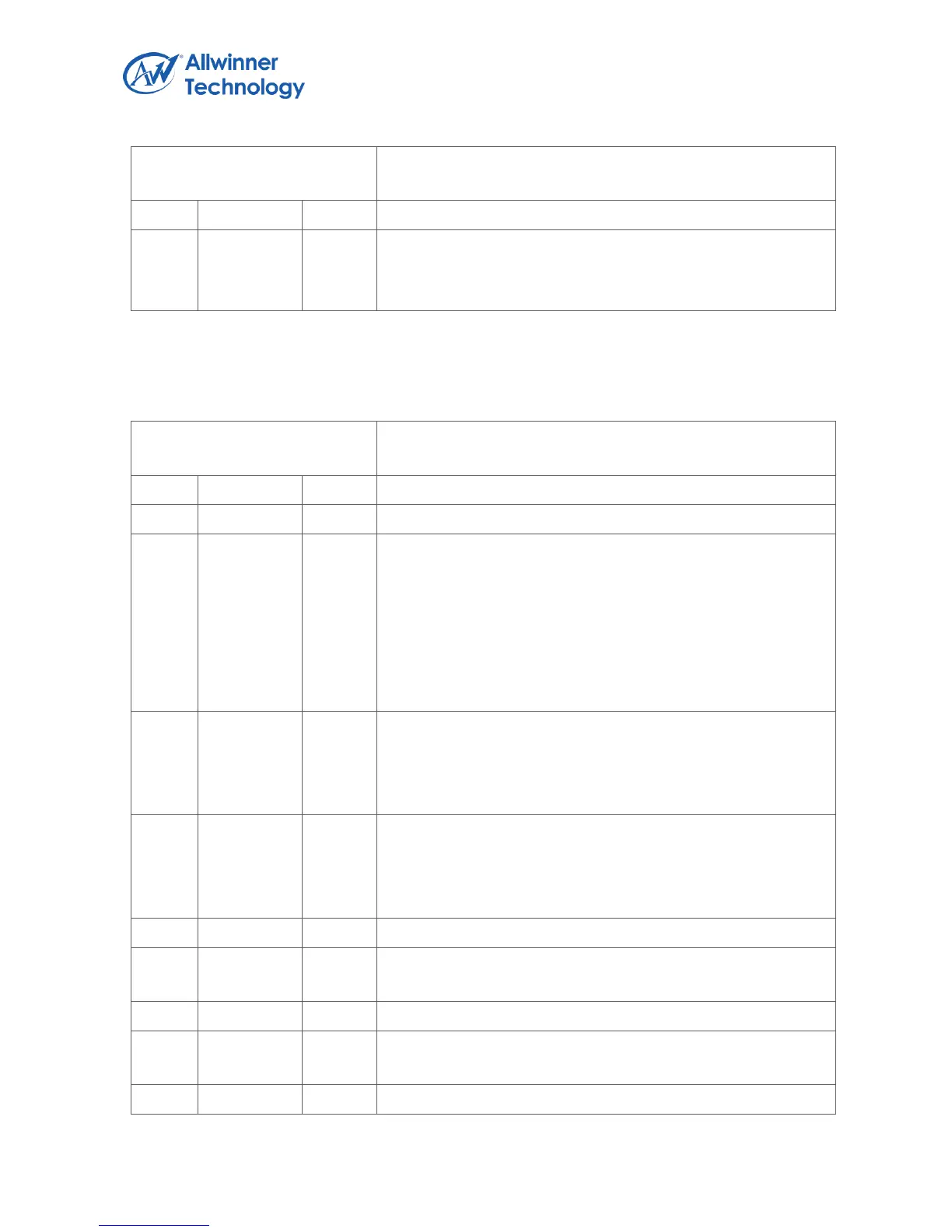

6.5.5.3. PS2 LINE CONTROL REGISTER

Register Name: PS2_LCTL

Default Value: 0x0000_0000

NO_ACK

ACK Control

0 – In Host function mode, must check ACK after transmitted

data; In Device function mode, must send ACK after received

data from Host.

1 – In Host function mode, don’t check ACK after transmitted

data; In Device function mode, don’t send ACK after received

data from Host.

FORCE_DATA

Force Data to LOW

0 – Data Line works in Normal Mode

1 – Data Line is forced to LOW

FORCE_CLK

Force Clock to LOW

0 – Clock Line works in Normal Mode

1 – Clock Line is forced to LOW

TXDTO_IEN

TX Data Timeout Interrupt Enable

STOP_IEN

Stop Error Interrupt Enable

Loading...

Loading...