A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 636 / 812

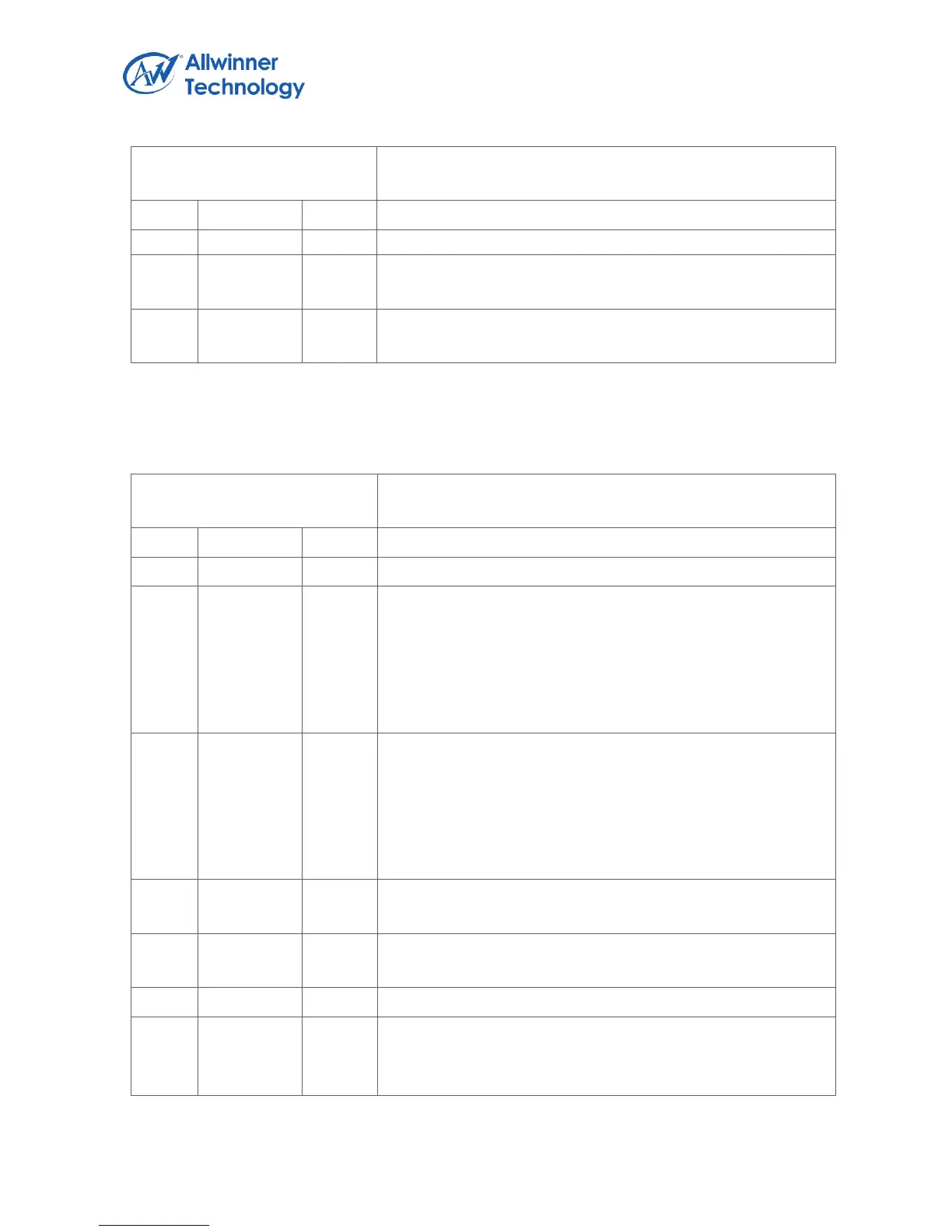

Register Name: PS2_LCTL

Default Value: 0x0000_0000

Acknowledge Error Interrupt Enable

PARERR_IEN

Parity Error Interrupt Enable

RXDTO_IEN

RX Data Timeout Interrupt Enable

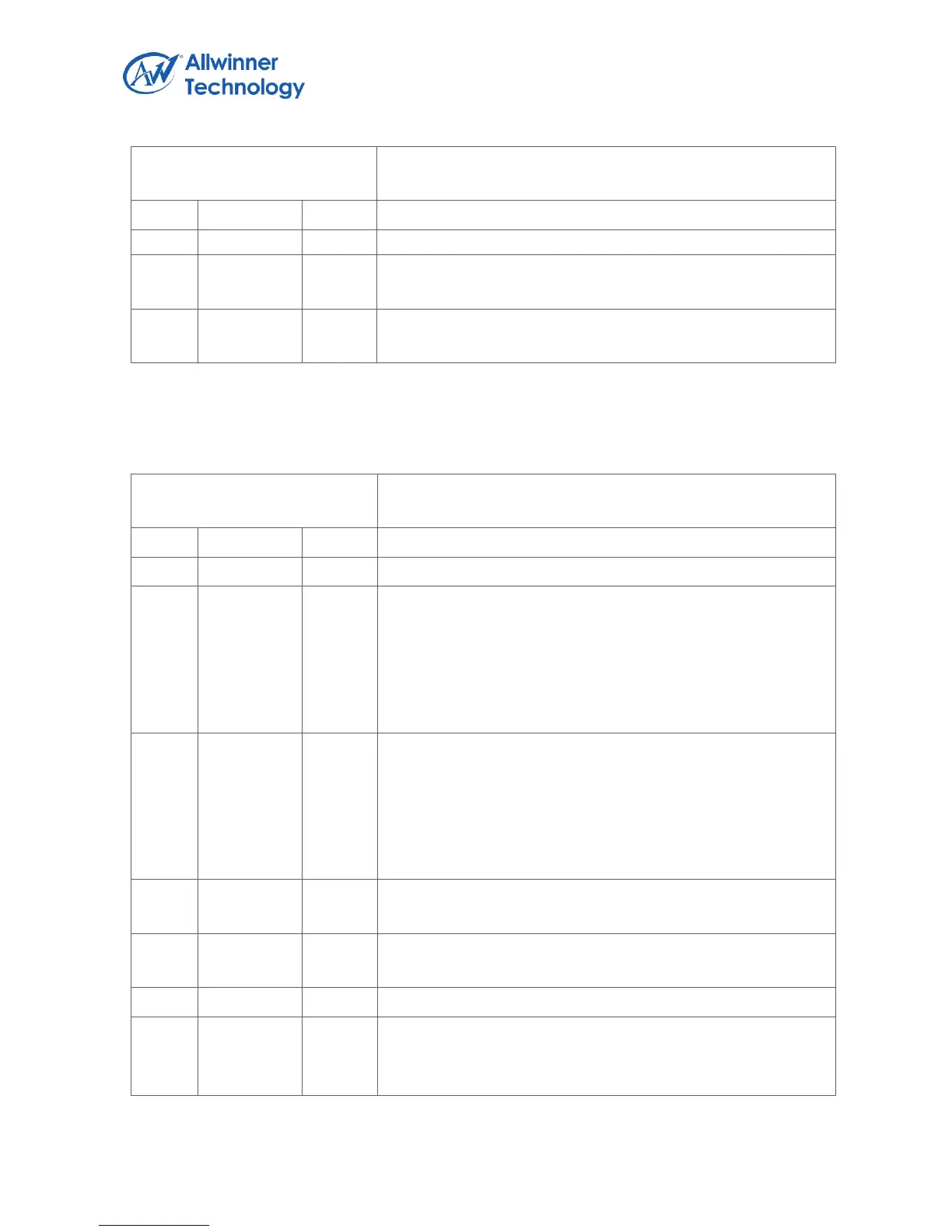

6.5.5.4. PS2 LINE STATUS REGISTER

Register Name: PS2_LSTS

Default Value: 0x0003_0000

TX_BUSY

Transmit Busy

0 – PS2 Module Transmit Engine is Idle.

1 – PS2 Module is currently sending data.

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

RX_BUSY

Receive Busy

0 –PS2 Module Receive Engine is Idle.

1 –PS2 Module is currently receiving data.

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

LS_DATA

Line State of DATA. Invalid before BUS_EN set.

LS_CLK

Line State of CLOCK. Invalid before BUS_EN set.

TX_DTO

Transmit Data Timeout

Timers include:

Loading...

Loading...