A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 637 / 812

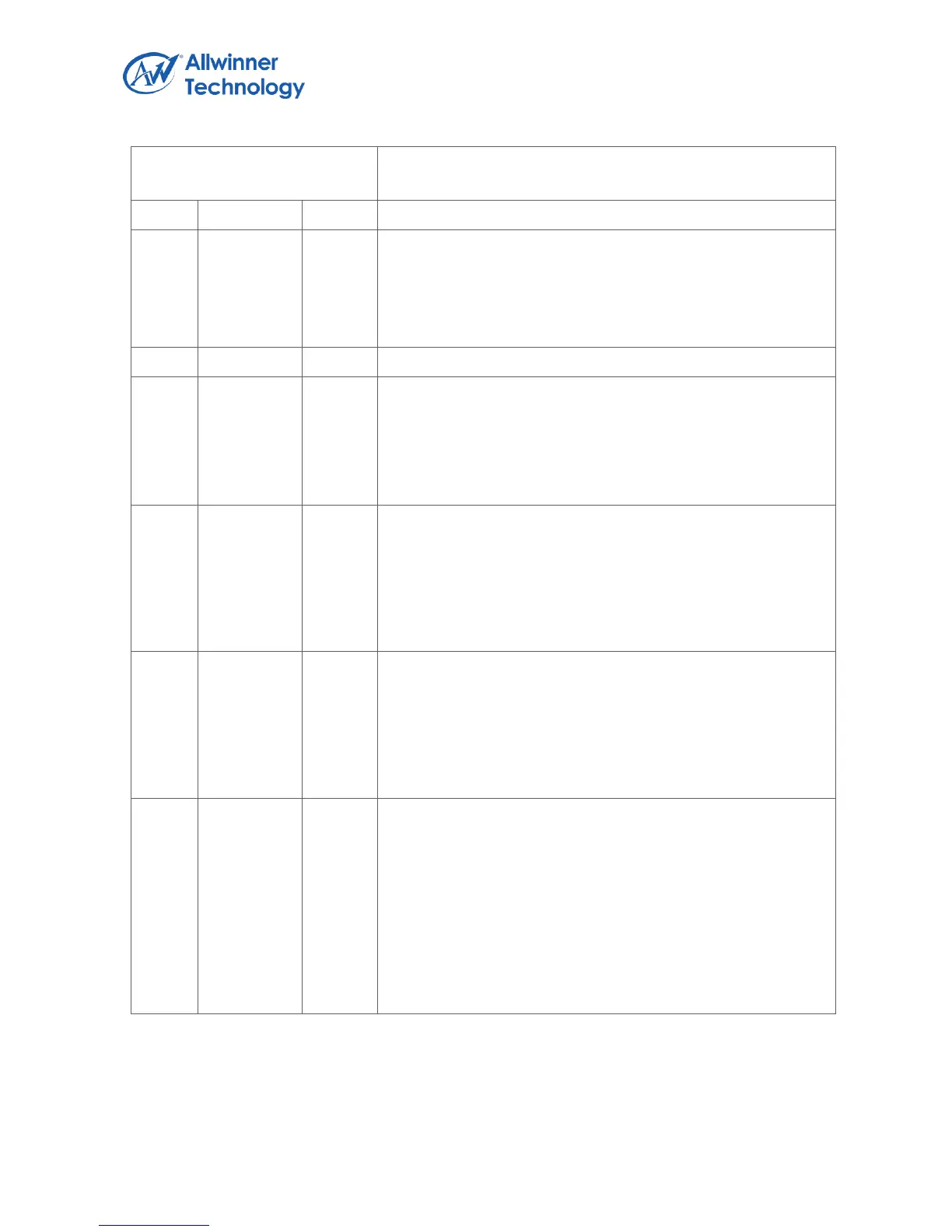

Register Name: PS2_LSTS

Default Value: 0x0003_0000

Tc2c<15ms (Host pull low Clock to Device drive Clock)

Tdata<2ms (Time for packet to send)

Tckl+Tckh<100us(one cycle time, as host)

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

STOP_ERR

Stop Bit Error

0 –No Error

1 –Stop Error

This bit can be cleared by writing ‘1’, writing ‘0’ has no effect.

ACK_ERR

Acknowledge Error

0 – ACK is received after data transmitted.

1 – ACK is not received after data transmitted.

Note: 1) Only for Master Function; 2) This bit can be cleared

by writing ‘1’, writing ‘0’ has no effect.

PAR_ERR

Parity Error

0 – No Error

1 – Parity Error

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

RX_DTO

Receive Data Timeout

Timers include:

Trsp<20ms(time from the host releases the Clock line to

device sends corresponding response)

Tckl+Tckh<100us(one cycle time, as host)

Note: This bit can be cleared by writing ‘1’, writing ‘0’ has no

effect.

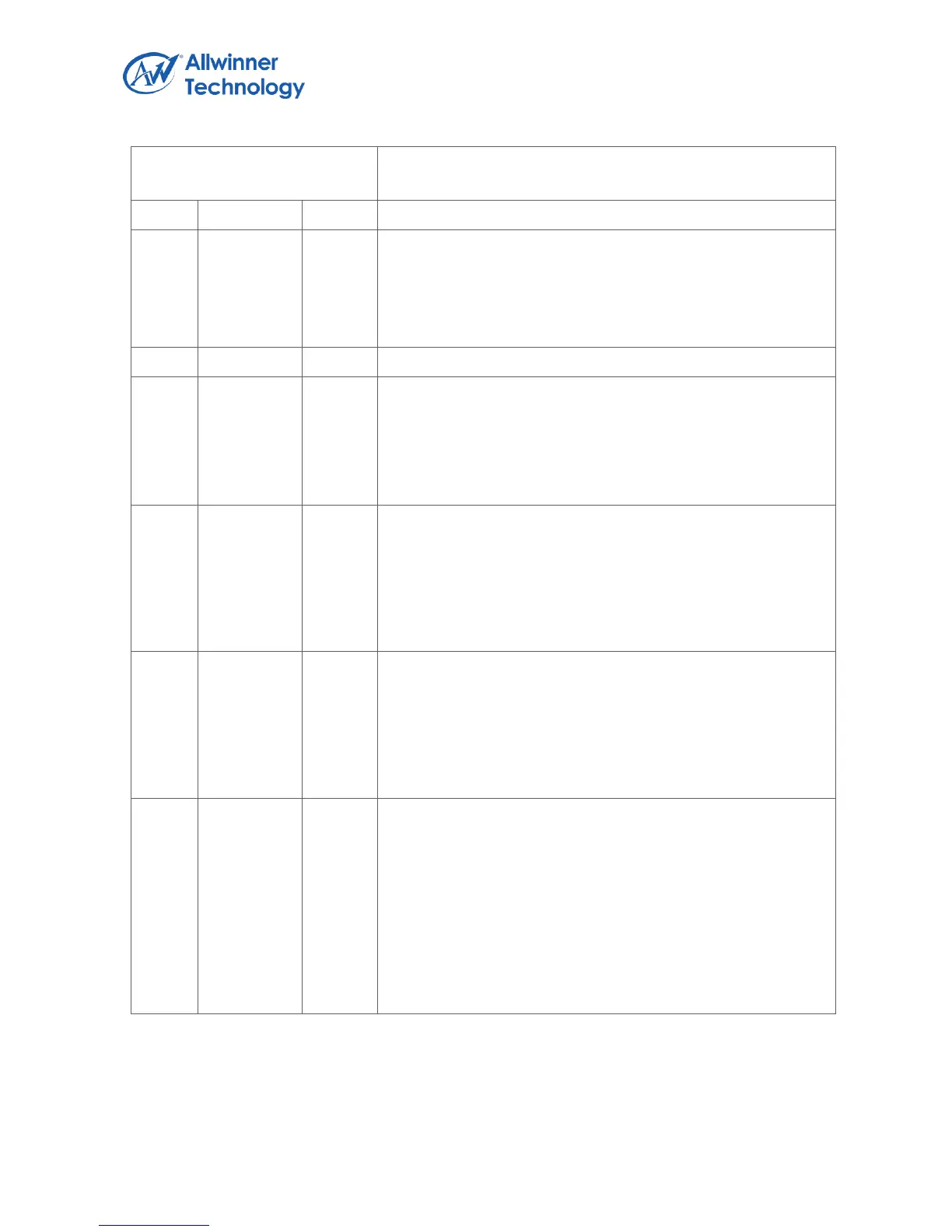

6.5.5.5. PS2 FIFO CONTROL REGISTER

Loading...

Loading...