A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 645 / 812

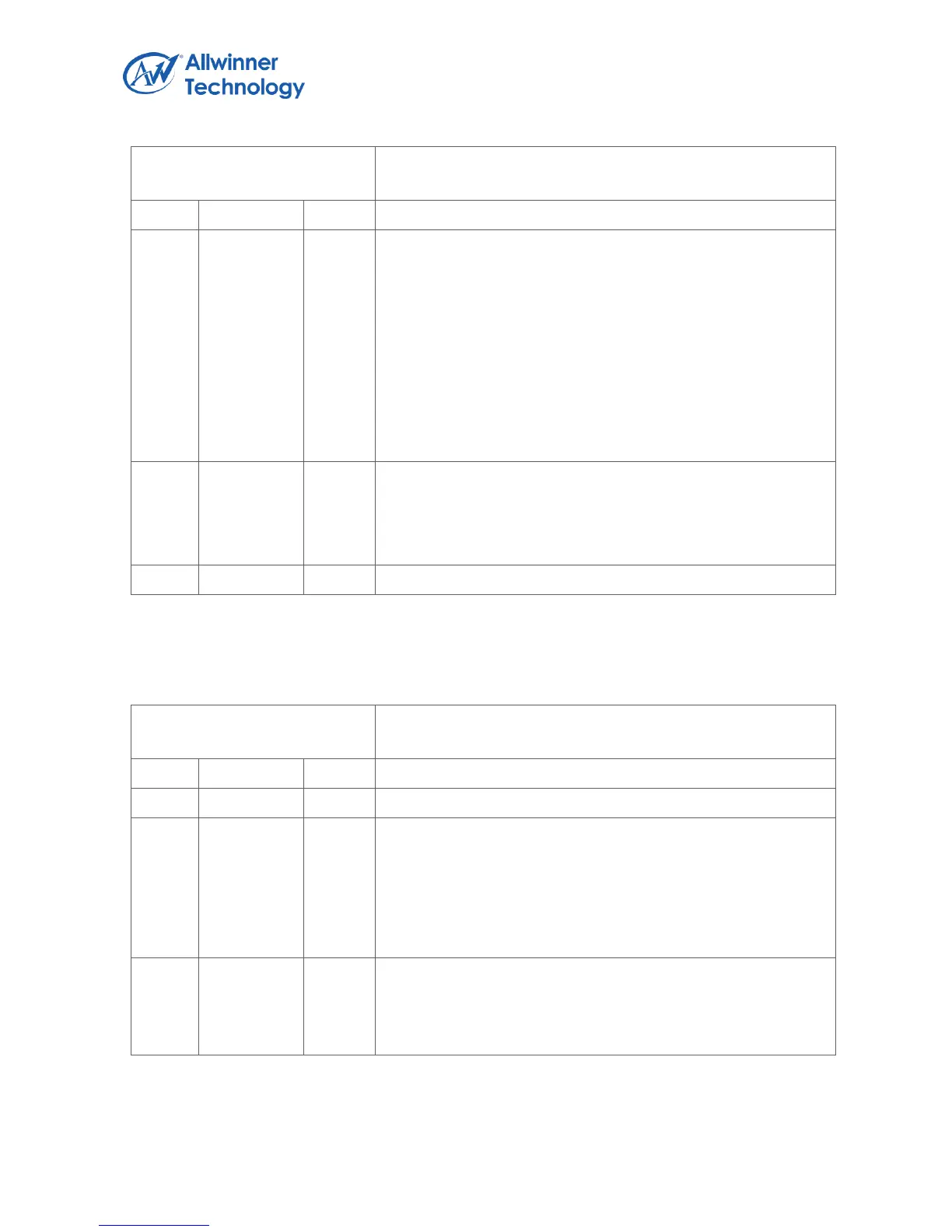

Register Name: IR_TXCTL

Default Value: 0x0000_0000

Transmit SIP

Writing ‘1’ to this bit produces a “Serial Infrared Interaction

Pulse” transmission.

Writing a ‘0’ to this bit is ignored. This bit is always read as “0”.

If this bit is set while in the middle of the transfer, the packet

will be ignored by IRDA controller.

Don’t Set SIP bit in the middle of transfer.

A SIP is defined as a 1.6us optical pulse of the transmitter

followed by a 7.1us off time of the transmitter. It simulates a start

pulse, causing the potentially interfering system to listen for at

least 500 ms.

TPPI

Transmit Pulse Polarity Invert

0: Not invert transmit pulse

1: Invert transmit pulse

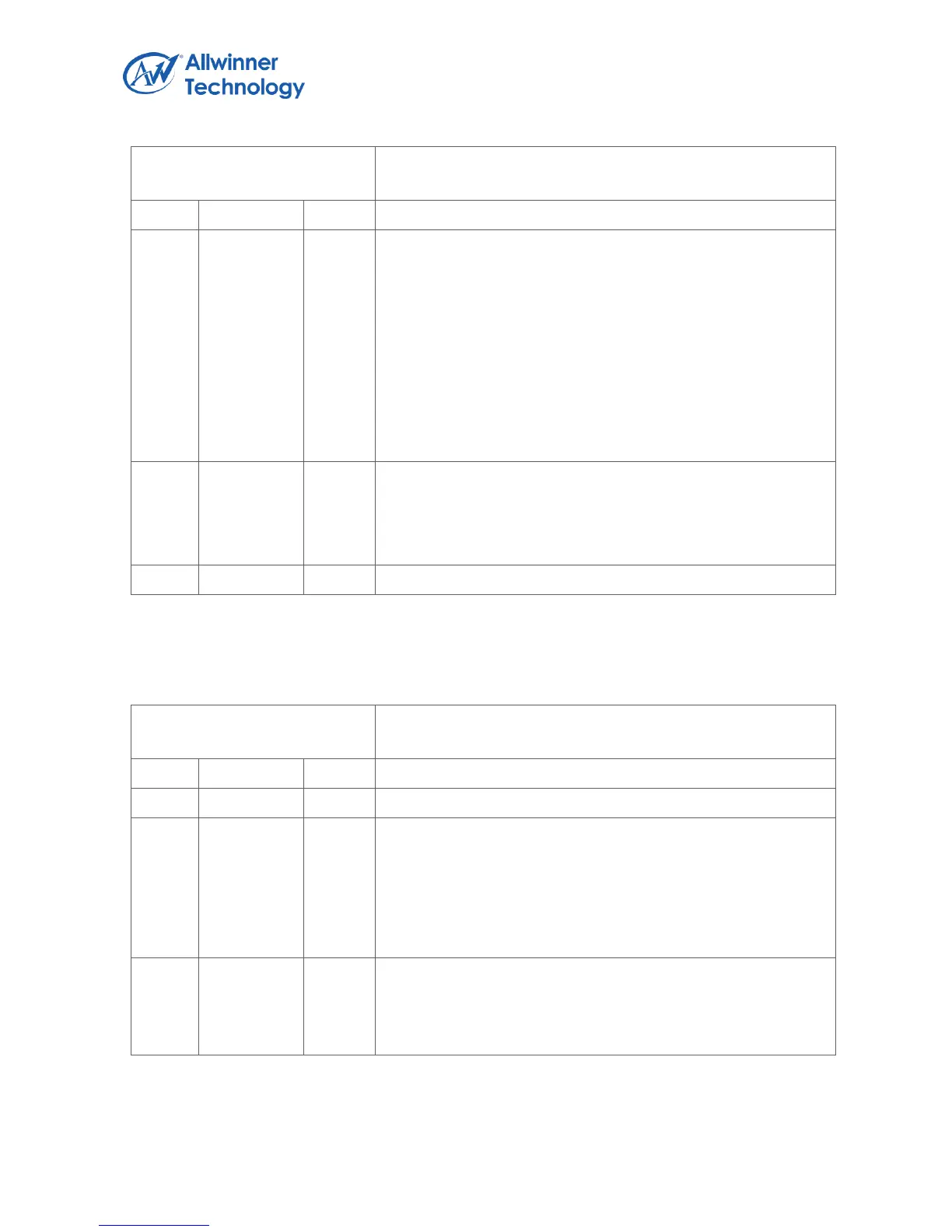

6.6.3.3. IR TRANSMITTER ADDRESS REGISTER

Register Name: IR_TXADR

Default Value: 0x0000_0000

HAG

Hardware Address Generator. When this bit is set, the content

of the TPA bits is transmitted as a packet address. When the

bit is cleared, the packet address is read from TX FIFO.

0: Read packet address from TX FIFO

1: Use TPA bits as packet address

TPA

Transmit Packet Address

This field contains the 8-bit Transmit Packet Address. If the

HAG bit is cleared, the TPA bits have no effect.

Loading...

Loading...