A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 666 / 812

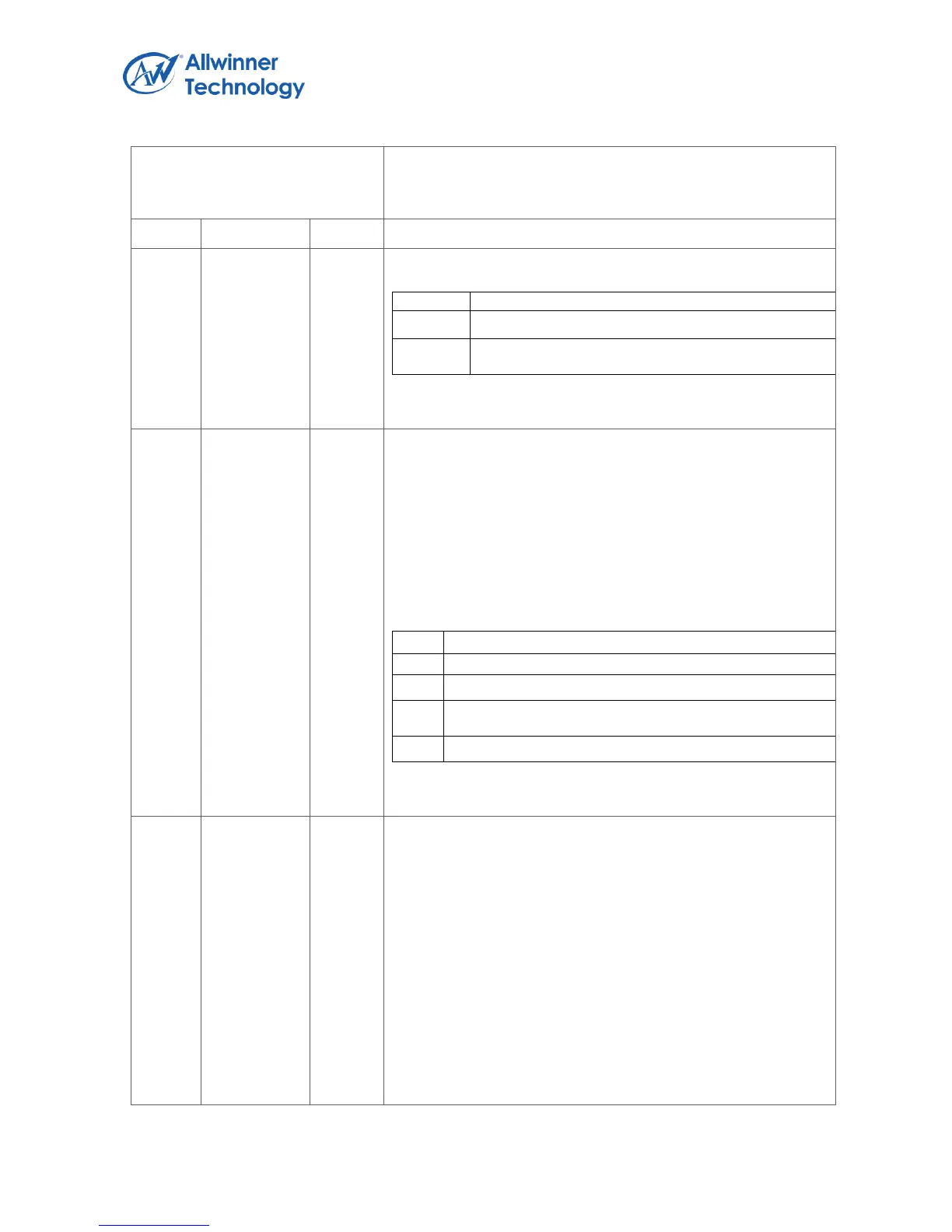

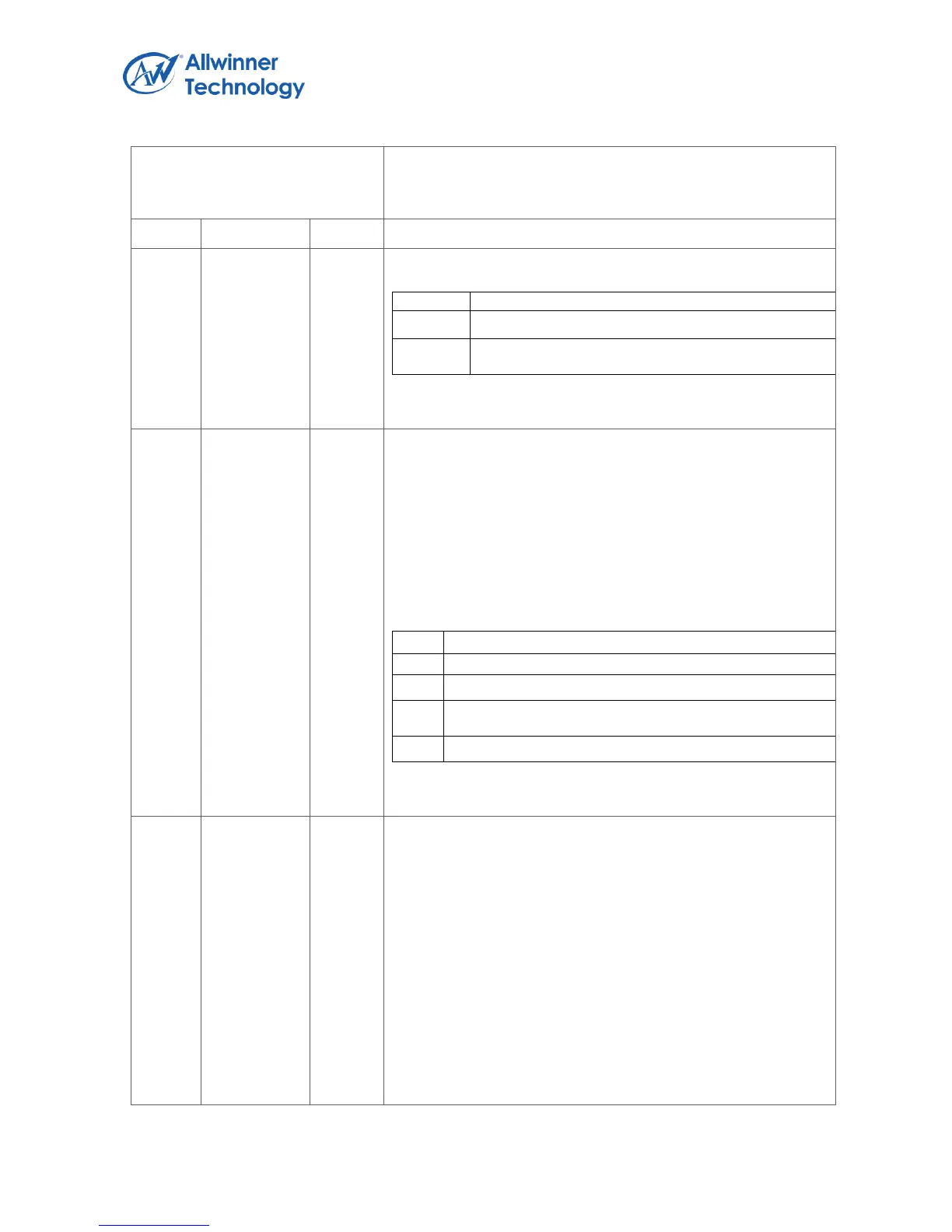

Register Name: USBCMD

Default Value: 0x00080000(0x00080B00 if Asynchronous

Schedule Park Capability is a one)

This bit controls whether the host controller skips processing

the Periodic Schedule. Values mean:

Do not process the Periodic Schedule.

Use the PERIODICLISTBASE register to access the

Periodic Schedule.

The default value of this field is ‘0b’.

FLS

Frame List Size

This field is R/W only if Programmable Frame List Flag in the

HCCPARAMS registers is set to a one. This field specifies

the size of the

Frame list. The size the frame list controls which bits in the

Frame Index

Register should be used for the Frame List Current index.

Values mean:

1024 elements(4096bytes)Default value

256 elements(1024bytes)For resource-constrained

condition

The default value is ‘00b’.

HCR

Host Controller Reset

This control bit is used by software to reset the host

controller. The effects of this on Root Hub registers are

similar to a Chip Hardware Reset.

When software writes a one to this bit, the Host Controller

resets its internal pipelines, timers, counters, state machines,

etc. to their initial value. Any transaction currently in progress

on USB is immediately terminated. A USB reset is not driven

on downstream ports.

All operational registers, including port registers and port

state machines are set to their initial values. Port ownership

reverts to the companion host controller(s). Software must

reinitialize the host controller as described in Section 4.1 of

Loading...

Loading...