A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 682 / 812

SchedulingOverrun in HcInterruptStatus has already been set.

This is used by HCD to monitor any persistent scheduling problem.

OwershipChangeRequest

This bit is set by an OS HCD to request a change of control of the

HC. When set HC will set the OwnershipChange field in

HcInterruptStatus. After the changeover, this bit is cleared and

remains so until the next request from OS HCD.

BulklListFilled

This bit is used to indicate whether there are any TDs on the Bulk

list. It is set by HCD whenever it adds a TD to an ED in the Bulk list.

When HC begins to process the head of the Bulk list, it checks

BLF. As long as BulkListFilled is 0, HC will not start processing

the Bulk list. If BulkListFilled is 1, HC will start processing the Bulk

list and will set BFL to 0. If HC finds a TD on the list, then HC will

set BulkListFilled to 1 causing the Bulk list processing to

continue. If no TD is found on the Bulk list, and if HCD does not set

BulkListFilled, then BulkListFilled will still be 0 when HC

completes processing the Bulk list and Bulk list processing will

stop.

ControlListFilled

This bit is used to indicate whether there are any TDs on the

Control list. It is set by HCD whenever it adds a TD to an ED in the

Control list.

When HC begins to process the head of the Control list, it checks

CLF. As long as ControlListFilled is 0, HC will not start

processing the Control list. If CLF is 1, HC will start processing the

Control list and will set ControlListFilled to 0. If HC finds a TD on

the list, then HC will set ControlListFilled to 1 causing the Control

list processing to continue. If no TD is found on the Control list, and

if the HCD does not set ControlListFilled, then ControlListFilled

will still be 0 when HC completes processing the Control list and

Control list processing will stop.

HostControllerReset

This bit is by HCD to initiate a software reset of HC. Regardless of

the functional state of HC, it moves to the USBSuspend state in

which most of the operational registers are reset except those

stated otherwise; e.g, the InteruptRouting field of HcControl, and

no Host bus accesses are allowed. This bit is cleared by HC upon

the completion of the reset operation. The reset operation must be

completed within 10 ms. This bit,

when set, should not cause a reset to the Root Hub and no

subsequent reset signaling should be asserted to its downstream

ports.

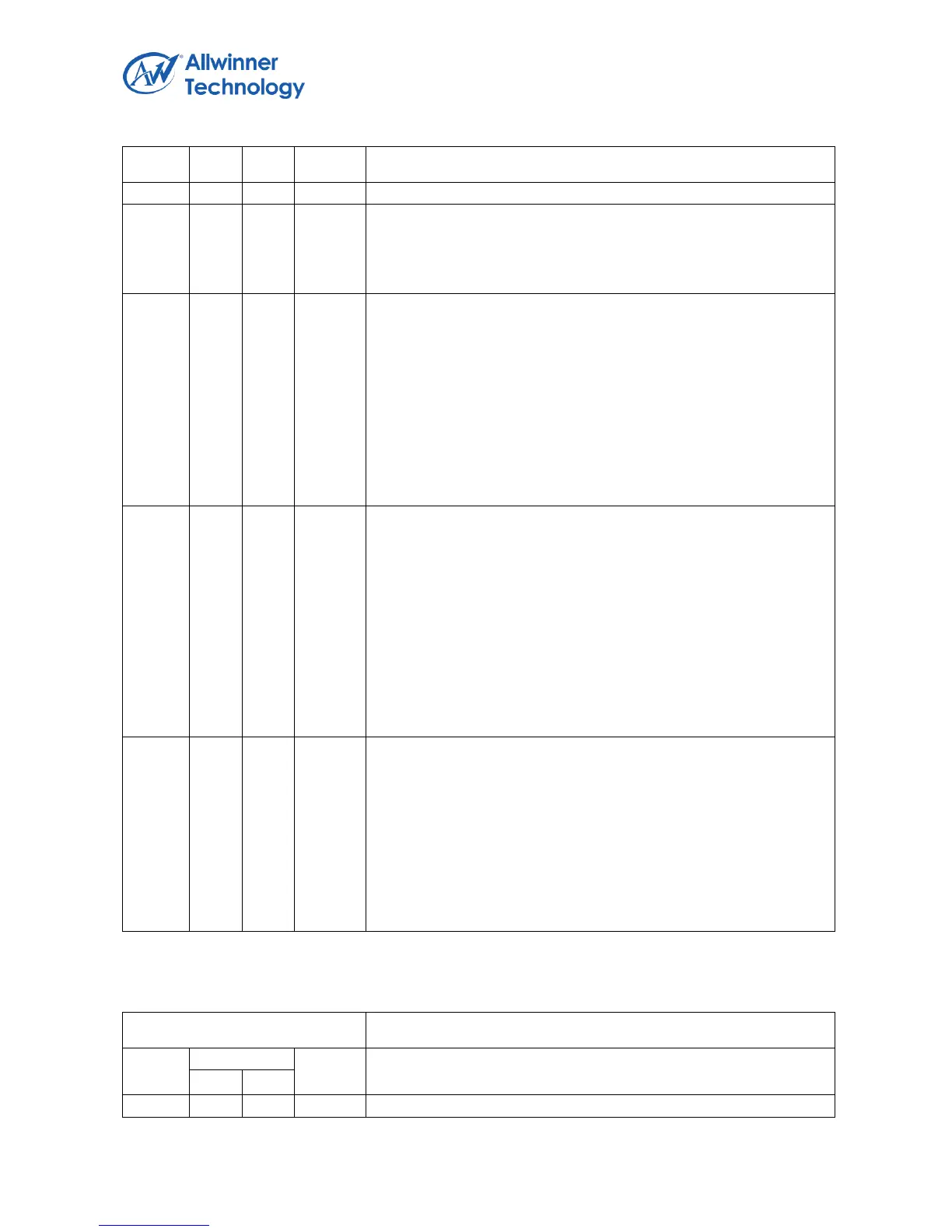

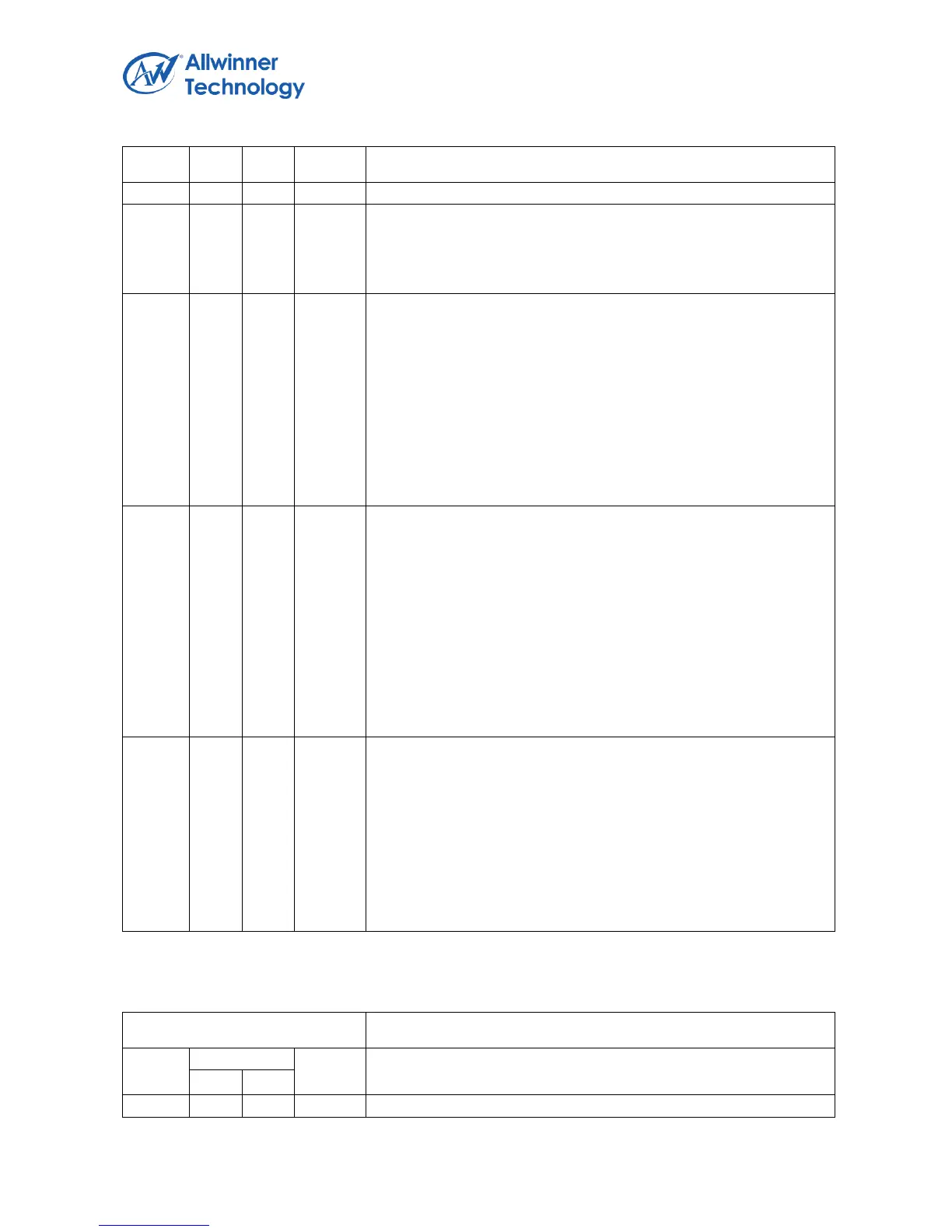

6.8.7.4. HCINTERRUPTSTATUS REGISTER

Register Name: HcInterruptStatus

Default Value:0x0

Loading...

Loading...