A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 683 / 812

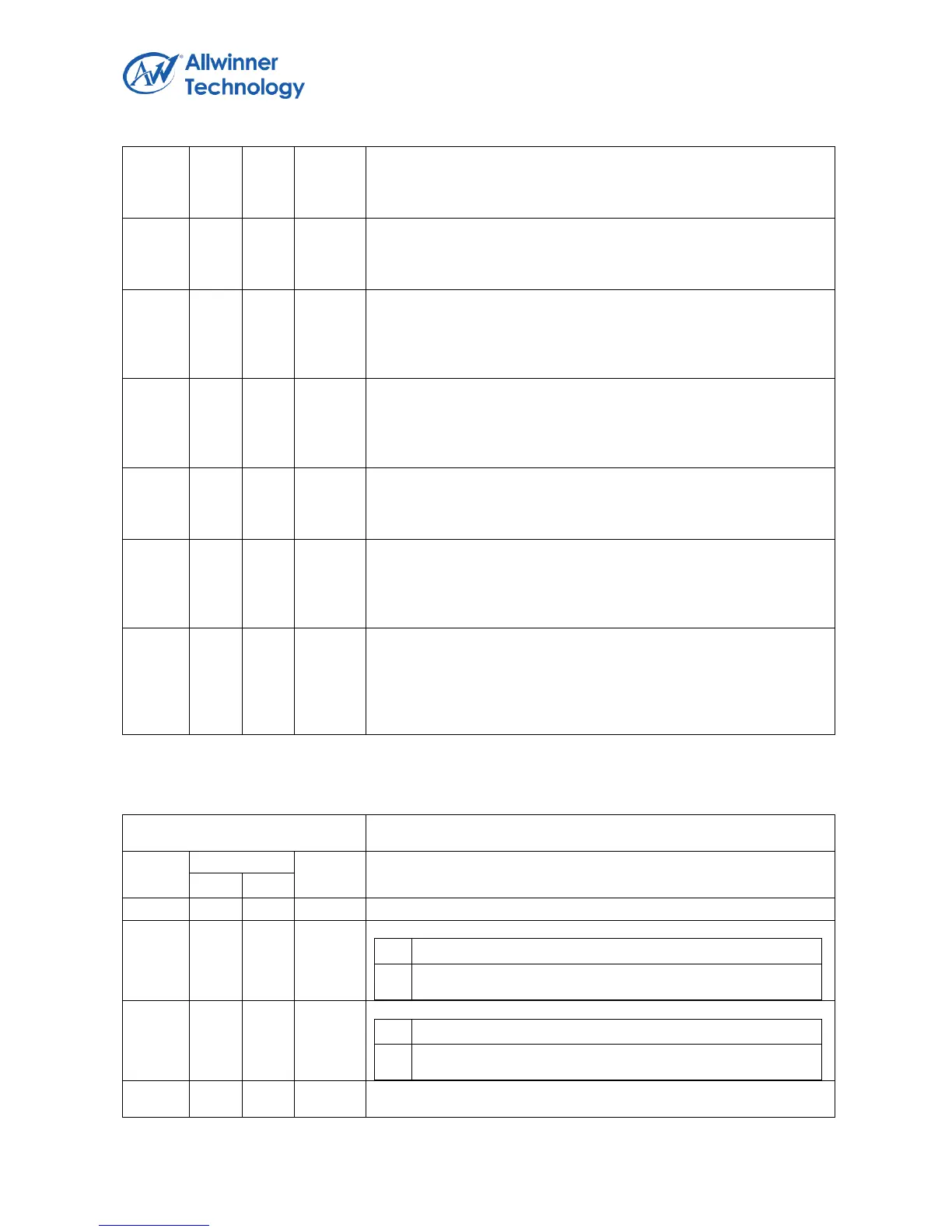

RootHubStatusChange

This bit is set when the content of HcRhStatus or the content of

any of HcRhPortStatus[NumberofDownstreamPort] has

changed.

FrameNumberOverflow

This bit is set when the MSb of HcFmNumber (bit 15) changes

value, from 0 to 1 or from 1 to 0, and after HccaFrameNumber has

been updated.

UnrecoverableError

This bit is set when HC detects a system error not related to USB.

HC should not proceed with any processing nor signaling before

the system error has been corrected. HCD clears this bit after HC

has been reset.

ResumeDetected

This bit is set when HC detects that a device on the USB is

asserting resume signaling. It is the transition from no resume

signaling to resume signaling causing this bit to be set. This bit is

not set when HCD sets the USBRseume state.

StartofFrame

This bit is set by HC at each start of frame and after the update of

HccaFrameNumber. HC also generates a SOF token at the same

time.

WritebackDoneHead

This bit is set immediately after HC has written HcDoneHead to

HccaDoneHead. Further updates of the HccaDoneHead will not

occur until this bit has been cleared. HCD should only clear this bit

after it has saved the content of HccaDoneHead.

SchedulingOverrun

This bit is set when the USB schedule for the current Frame

overruns and after the update of HccaFrameNumber. A scheduling

overrun will also cause the SchedulingOverrunCount of

HcCommandStatus to be

Incremented.

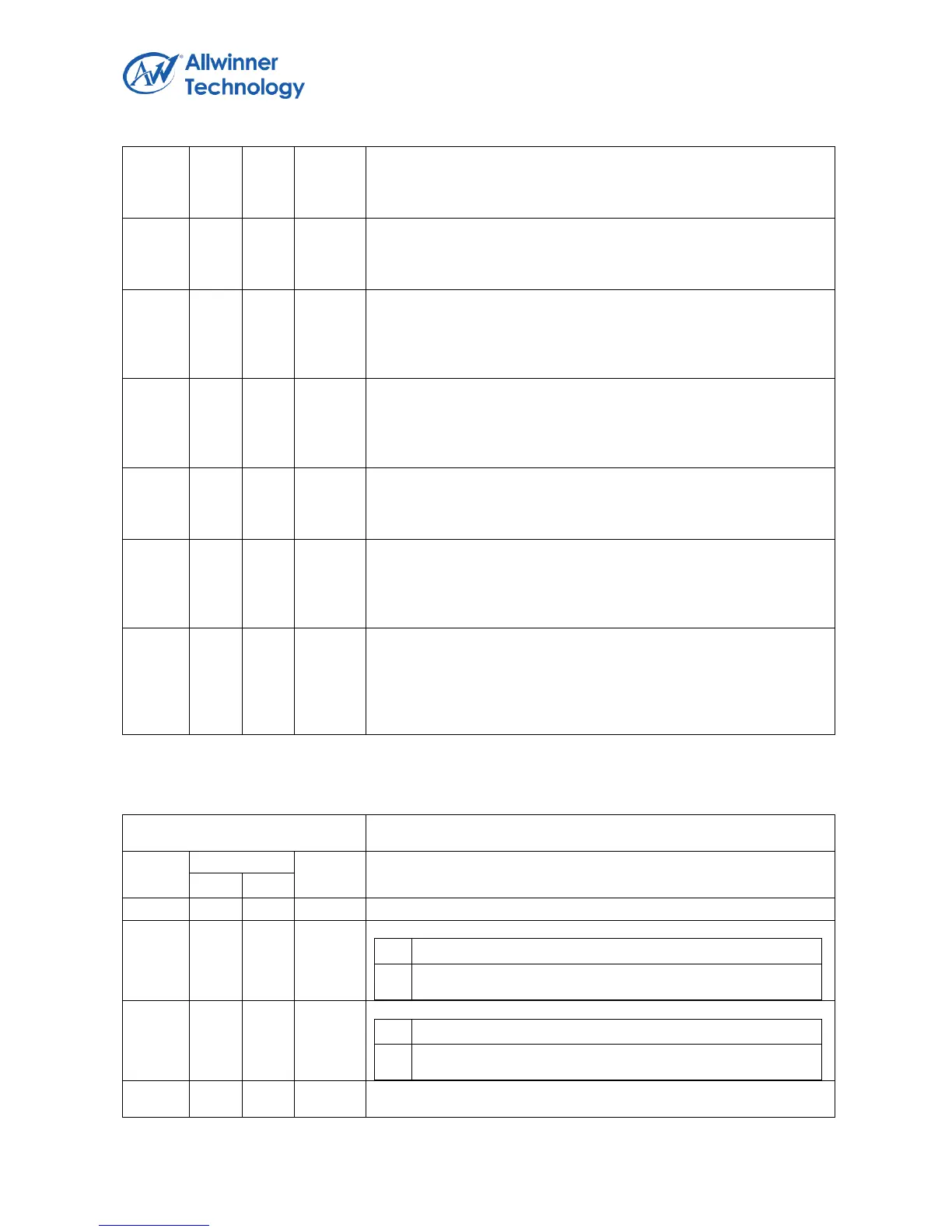

6.8.7.5. HCINTERRUPTENABLE REGISTER

Register Name: HcInterruptEnable Register

Default Value: 0x0

RootHubStatusChange Interrupt Enable

Enable interrupt generation due to Root Hub Status

Change;

FrameNumberOverflow Interrupt Enable

Enable interrupt generation due to Frame Number Over

Flow;

UnrecoverableError Interrupt Enable

Loading...

Loading...