A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 706 / 812

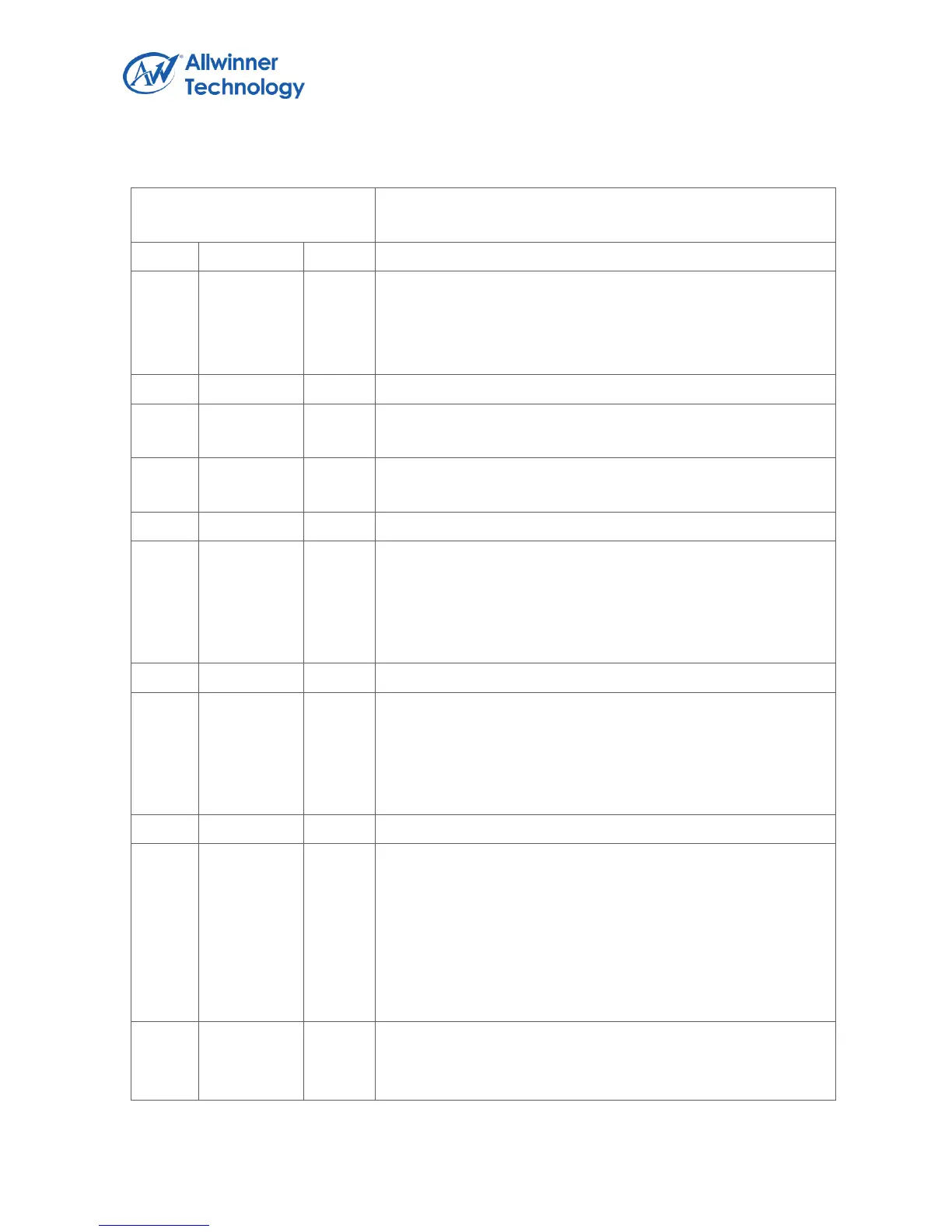

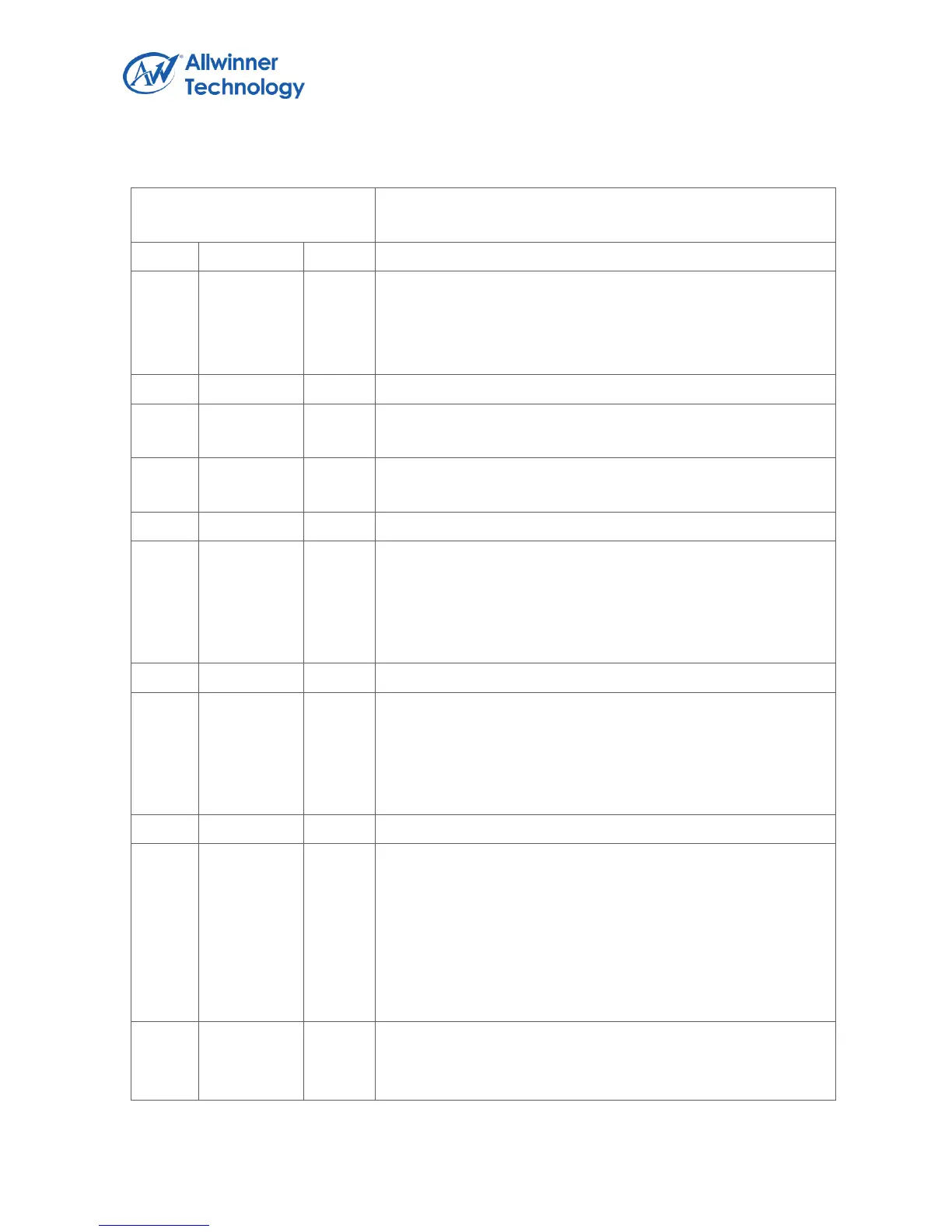

6.9.5.6. DIGITAL AUDIO FIFO CONTROL REGISTER

Register Name: DA_FCTL

Default Value: 0x0004_00F0

FIFOSRC

TX FIFO source select

0: APB bus

1: Analog Audio CODEC

FTX

Write ‘1’ to flush TX FIFO, self clear to ‘0’.

FRX

Write ‘1’ to flush RX FIFO, self clear to ‘0’.

TXTL

TX FIFO Empty Trigger Level

Interrupt and DMA request trigger level for TXFIFO normal

condition

Trigger Level = TXTL

RXTL

RX FIFO Trigger Level

Interrupt and DMA request trigger level for RXFIFO normal

condition

Trigger Level = RXTL + 1

TXIM

TX FIFO Input Mode (Mode 0, 1)

0: Valid data at the MSB of TXFIFO register

1: Valid data at the LSB of TXFIFO register

Example for 20-bits transmitted audio sample:

Mode 0: FIFO_I[23:0] = {4’h0, TXFIFO[31:12]}

Mode 1: FIFO_I[23:0] = {4’h0, TXFIFO[19:0]}

RXOM

RX FIFO Output Mode (Mode 0, 1, 2, 3)

00: Expanding ‘0’ at LSB of DA_RXFIFO register.

Loading...

Loading...