A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 753 / 812

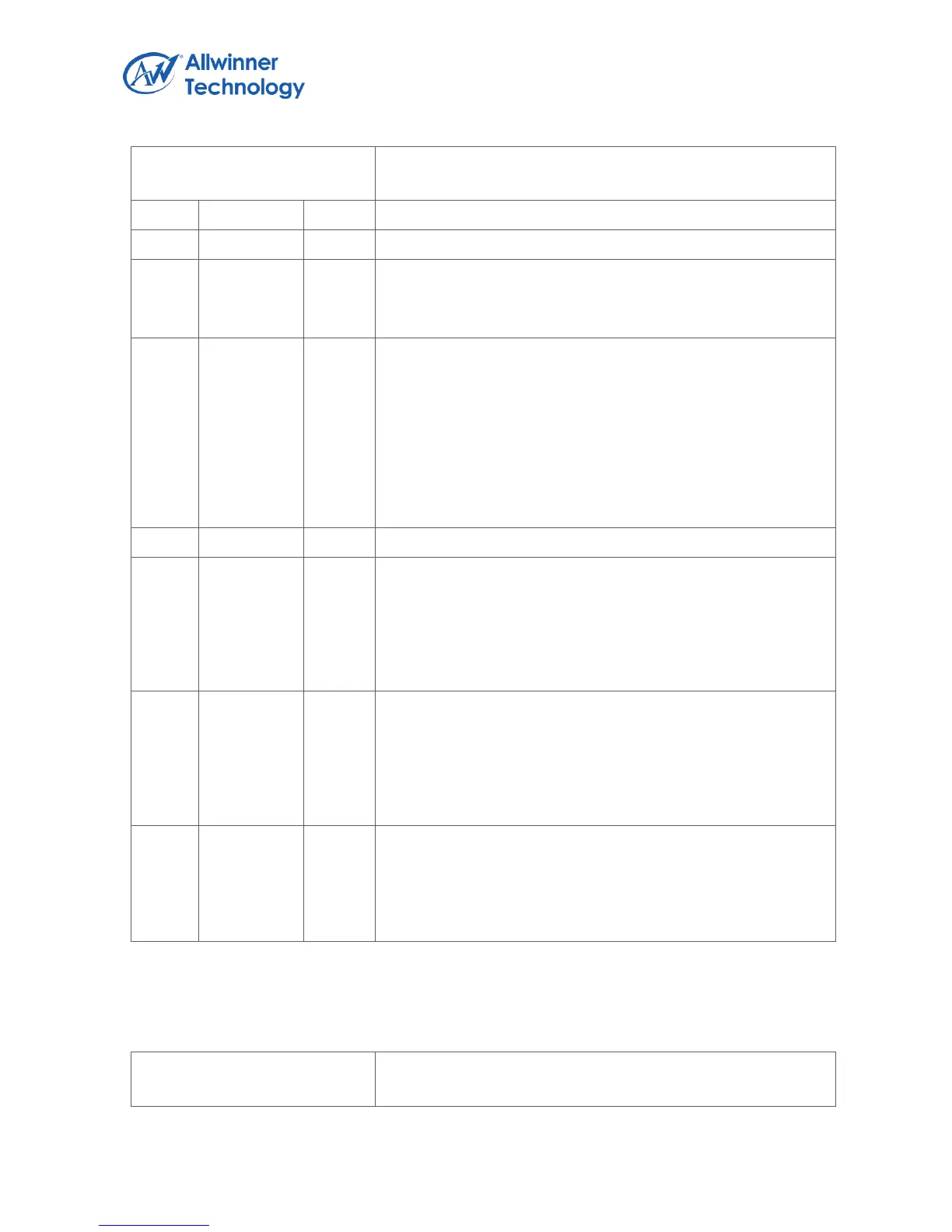

Register Name: TSG_CSR

Default Value: 0x0000_0000

TSGLBufMode

Loop Buffer Mode

When set to ‘1’, the TSG external buffer is in loop mode.

TSGSyncByteChkEn

Sync Byte Check Enable

Enable/ Disable check SYNC byte fro receiving new packet

0: Disable

1: Enable

If enable check SYNC byte and an error SYNC byte is

receiver, TS Generator would come into PAUSE state. If the

correspond interrupt is enable, the interrupt would happen.

TSGPauseBit

Pause Bit for TS Generator

Write ‘1’ to pause TS Generator. TS Generator would stop

fetch new data from DRAM. After finishing this operation, this

bit will clear to zero by hardware. In PAUSE state, write ‘1’ to

resume this state.

TSGStopBit

Stop Bit for TS Generator

Write ‘1’ to stop TS Generator. TS Generator would stop fetch

new data from DRAM. The data already in its FIFO should be

sent to TS filter. After finishing this operation, this bit will clear

to zero by hardware.

TSGStartBit

Start Bit for TS Generator

Write ‘1’ to start TS Generator. TS Generator would fetch data

from DRAM and generate SPI stream to TS filter. This bit will

clear to zero by hardware after TS Generator is running.

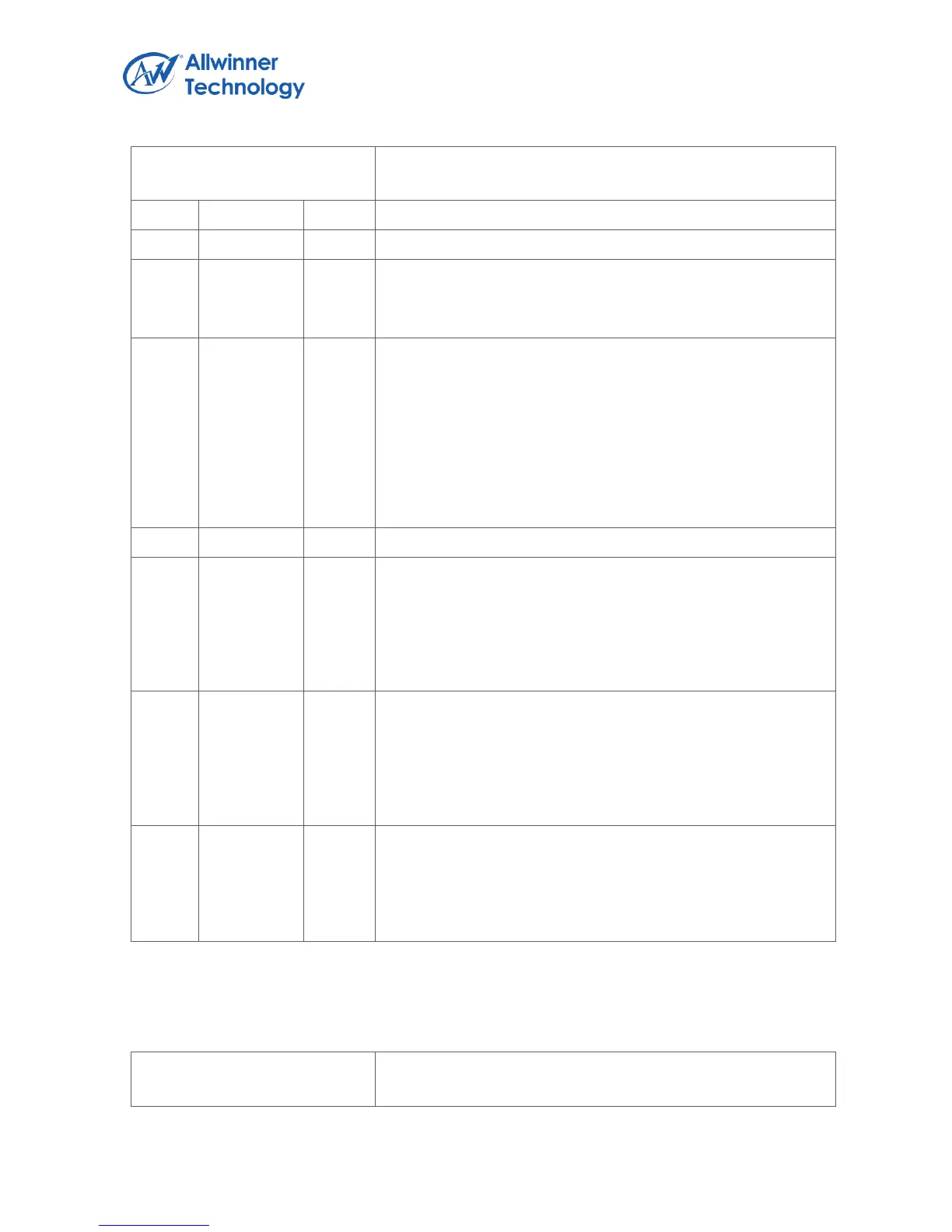

6.13.4.8. TSG PACKET PARAMETER REGISTER

Register Name: TSG_PPR

Default Value: 0x0000_0000

Loading...

Loading...