A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 755 / 812

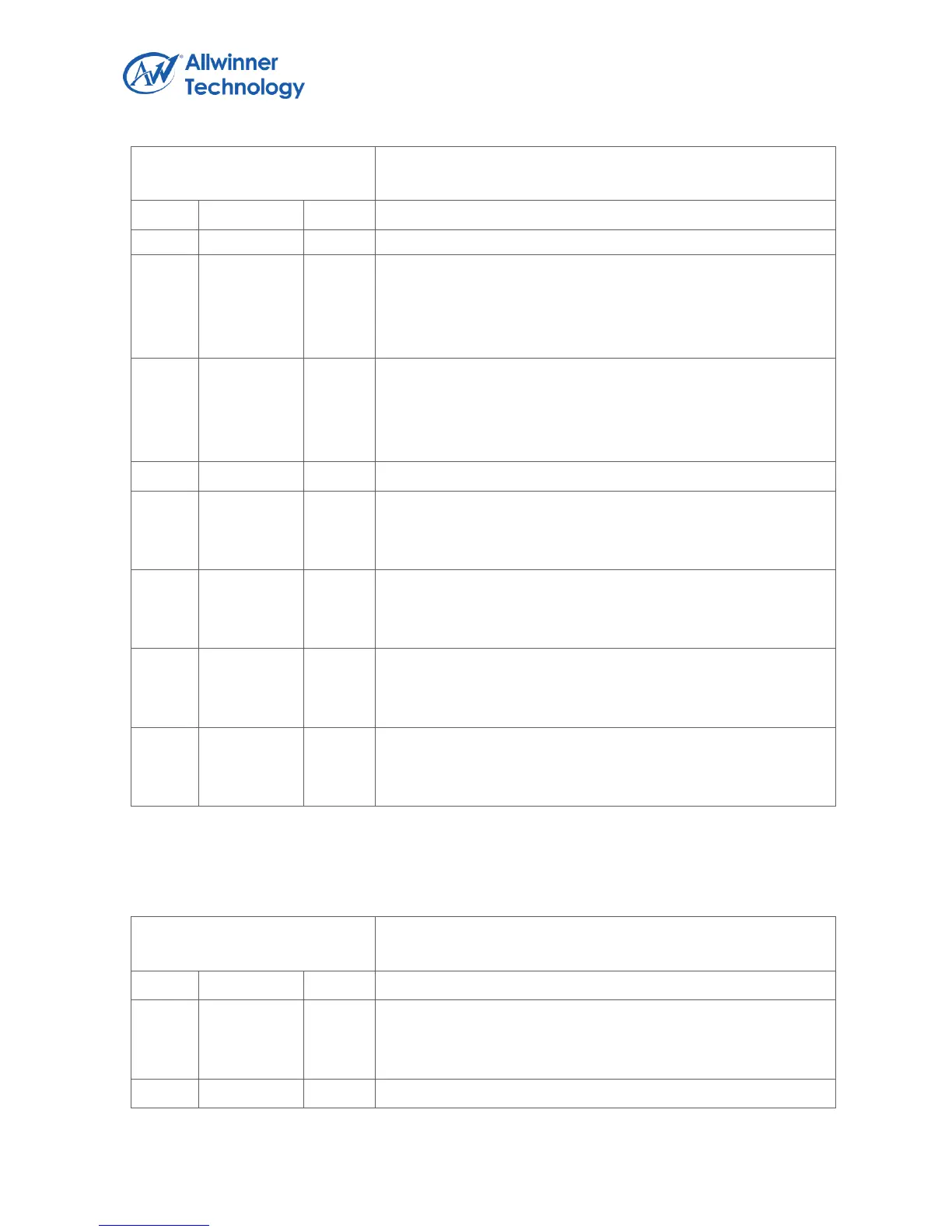

Register Name: TSG_IESR

Default Value: 0x0000_0000

TSGHFIE

TS Generator (TSG) Half Finish Interrupt Enable

0: Disable

1: Enable

TSGErrSyncByteIE

TS Generator (TSG) Error Sync Byte Interrupt Enable

0: Disable

1: Enable

TSGEndSts

TS Generator (TSG) End Status

Write ‘1’ to clear.

TSGFFSts

TS Generator (TSG) Full Finish Status

Write ‘1’ to clear.

TSGHFSts

TS Generator (TSG) Half Finish Status

Write ‘1’ to clear.

TSGErrSyncByteSts

TS Generator (TSG) Error Sync Byte Status

Write ‘1’ to clear.

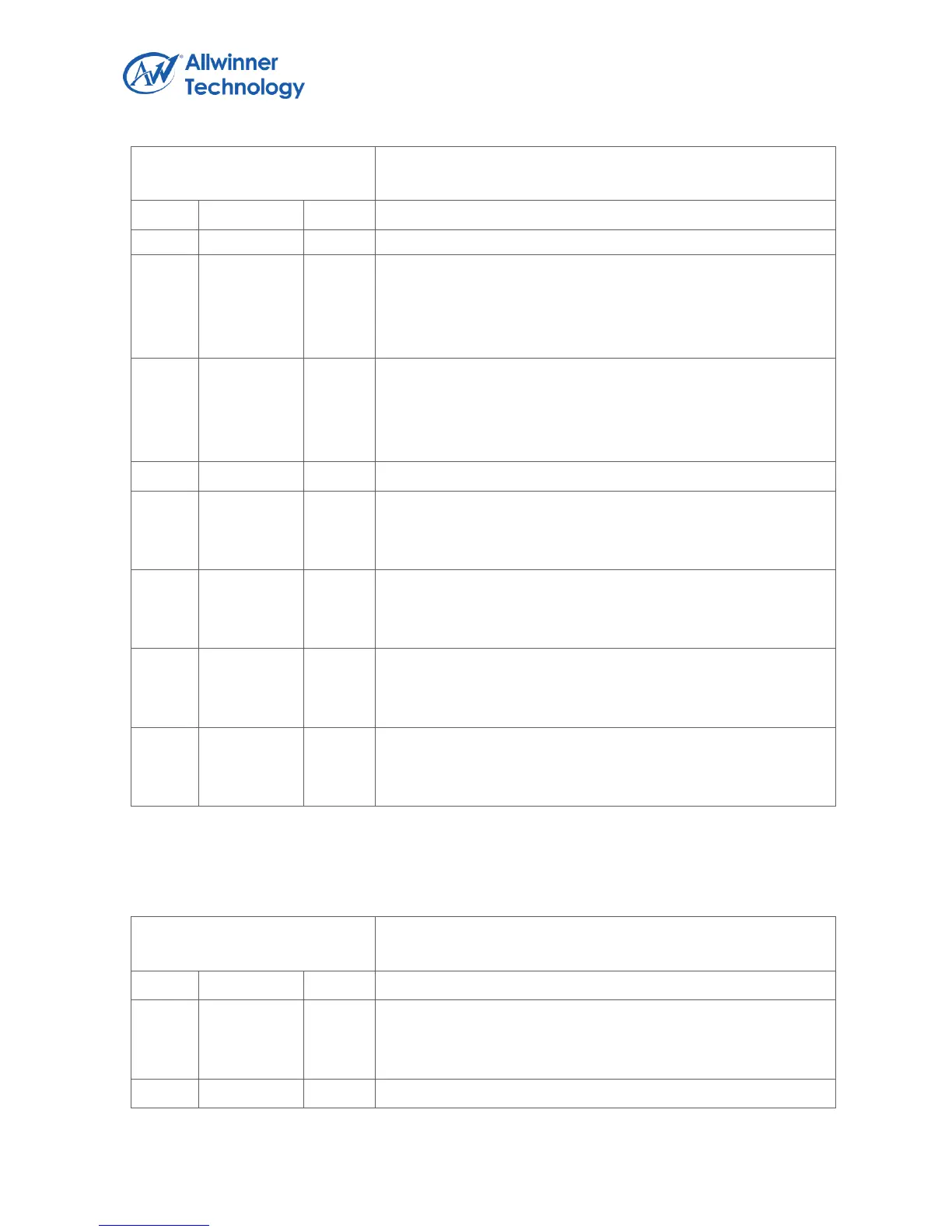

6.13.4.10. TSG CLOCK CONTROL REGISTER

Register Name: TSG_CCR

Default Value: 0x0000_0000

TSGCDF_N

TSG Clock Divide Factor (N)

The Numerator part of TSG Clock Divisor Factor.

Loading...

Loading...