A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 779 / 812

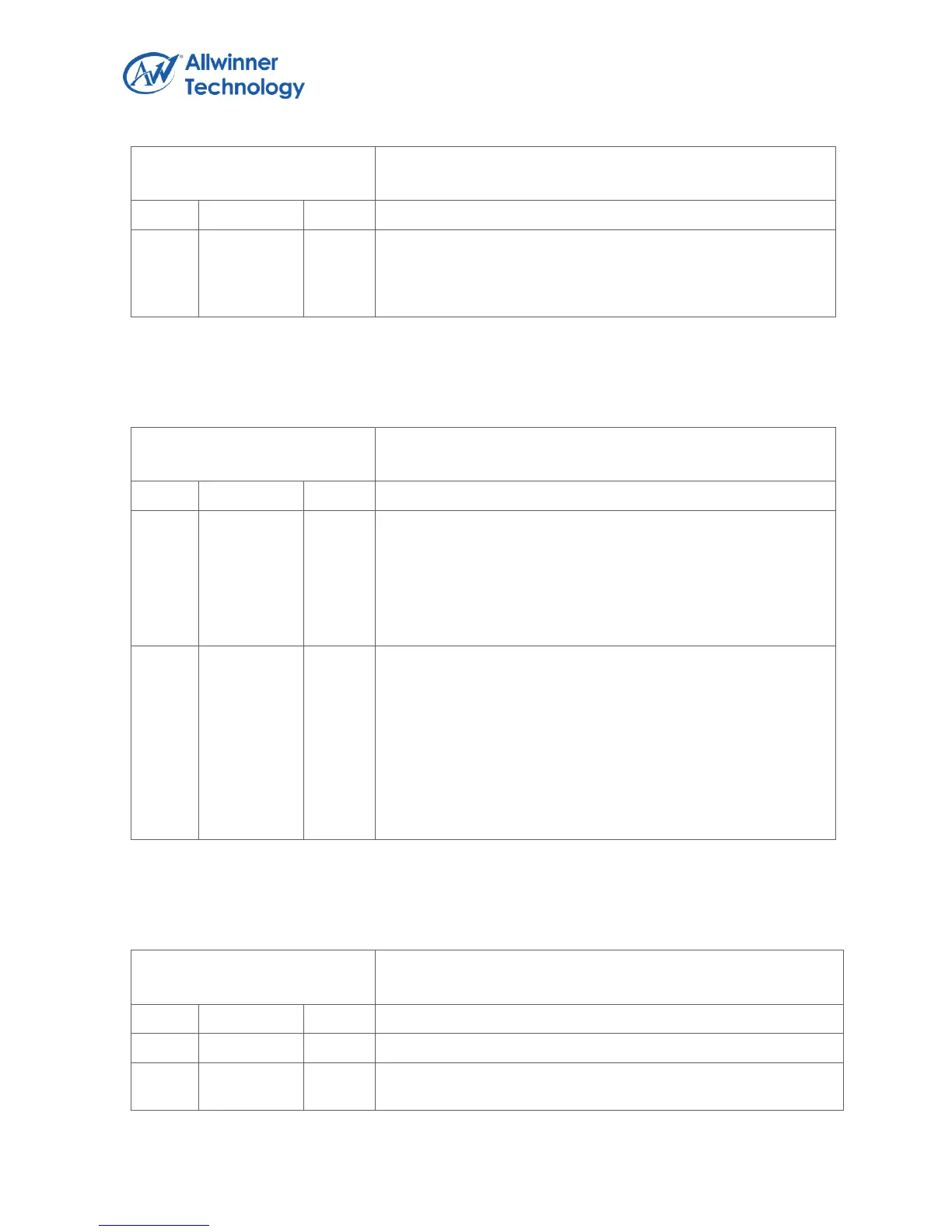

Register Name: SCR_REPEAT

Default Value: 0x00000000

TX Repeat

This is a 4-bit register that specifies the number of attempts to

re-transmit the character after the Smart Card signals the

wrong parity during the guard time.

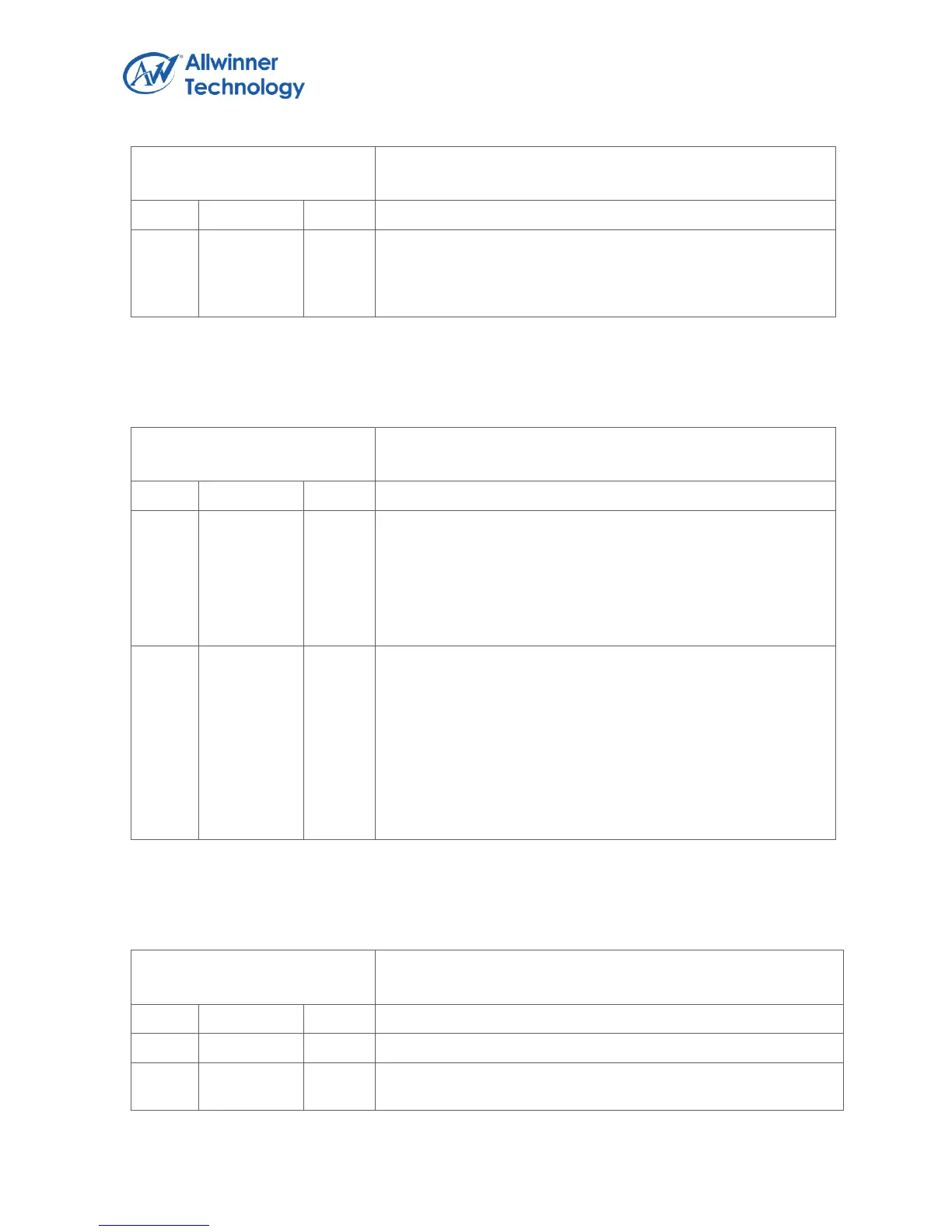

6.14.5.7. SMART CARD READER CLOCK DIVISOR REGISTER

Register Name: SCR_CLKDIV

Default Value: 0x00000000

BAUDDIV

Baud Clock Divisor. This 16-bit register defines the divisor

value used to generate the Baud Clock impulses from the

system clock.

SCCDIV

Smart Card Clock Divisor. This 16-bit register defines the

divisor value used to generate the Smart Card Clock from the

system clock.

is the frequency of Smart Card Clock Signal.

is the frequency of APB Clock.

6.14.5.8. SMART CARD READER LINE TIME REGISTER

Register Name: SCR_LTIM

Default Value: 0x00000000

ATR

ATR Start Limit. This 16-bit register defines the maximum time

Loading...

Loading...