A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 780 / 812

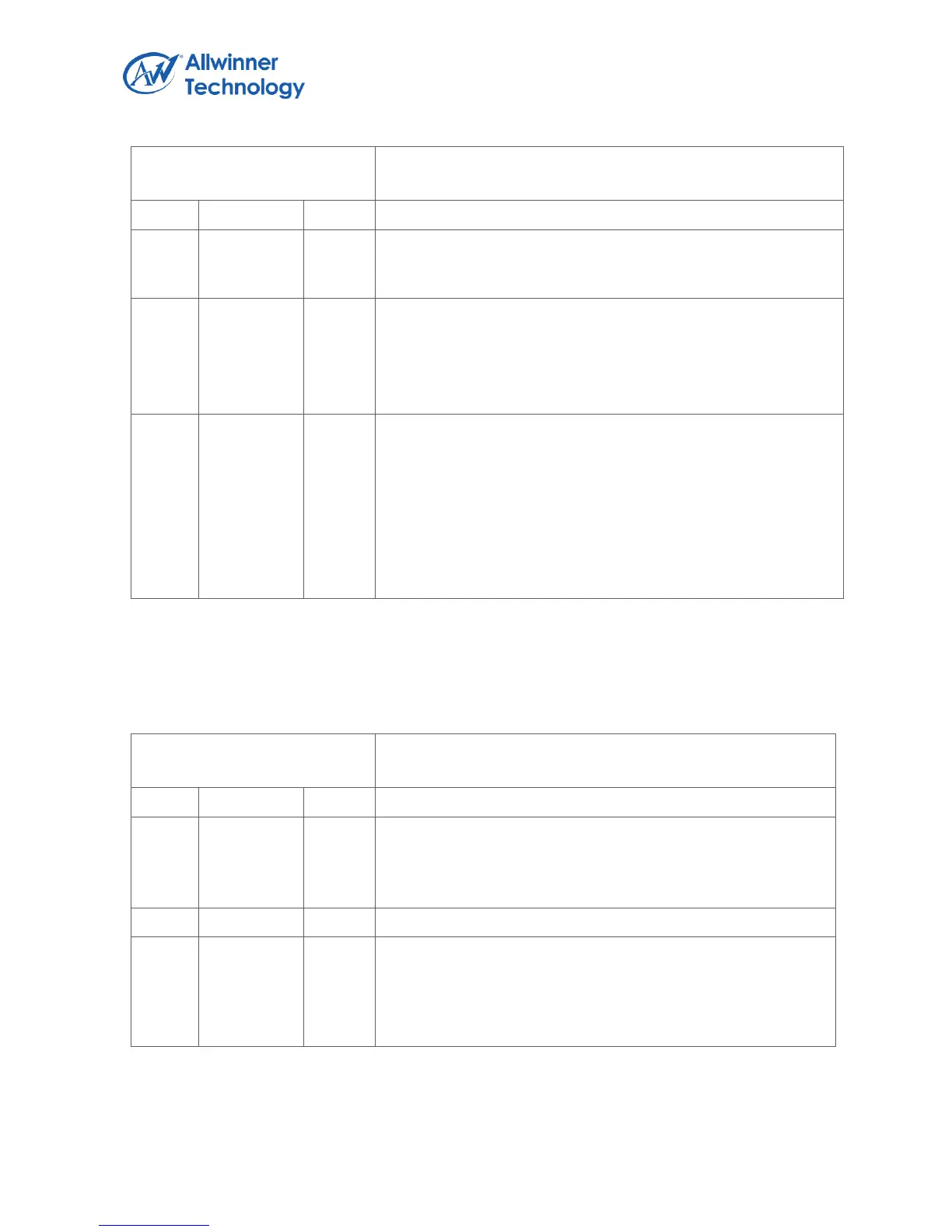

Register Name: SCR_LTIM

Default Value: 0x00000000

between the rising edge of the scrstn signal and the start of ATR

response.

ATR Start Limit = 128* ATR*.

RST

Reset Duration. This 16-bit register sets the duration of the

Smart Card reset sequence. This value is same for the cold and

warm reset.

Cold/Warm Reset Duration = 128* RST*.

ACT

Activation/Deactivation Time. This 16-bit register sets the

duration of each part of the activation and deactivation

sequence.

Activation/Deactivation Duration = 128* ACT *.

is the Smart Card Clock Cycle.

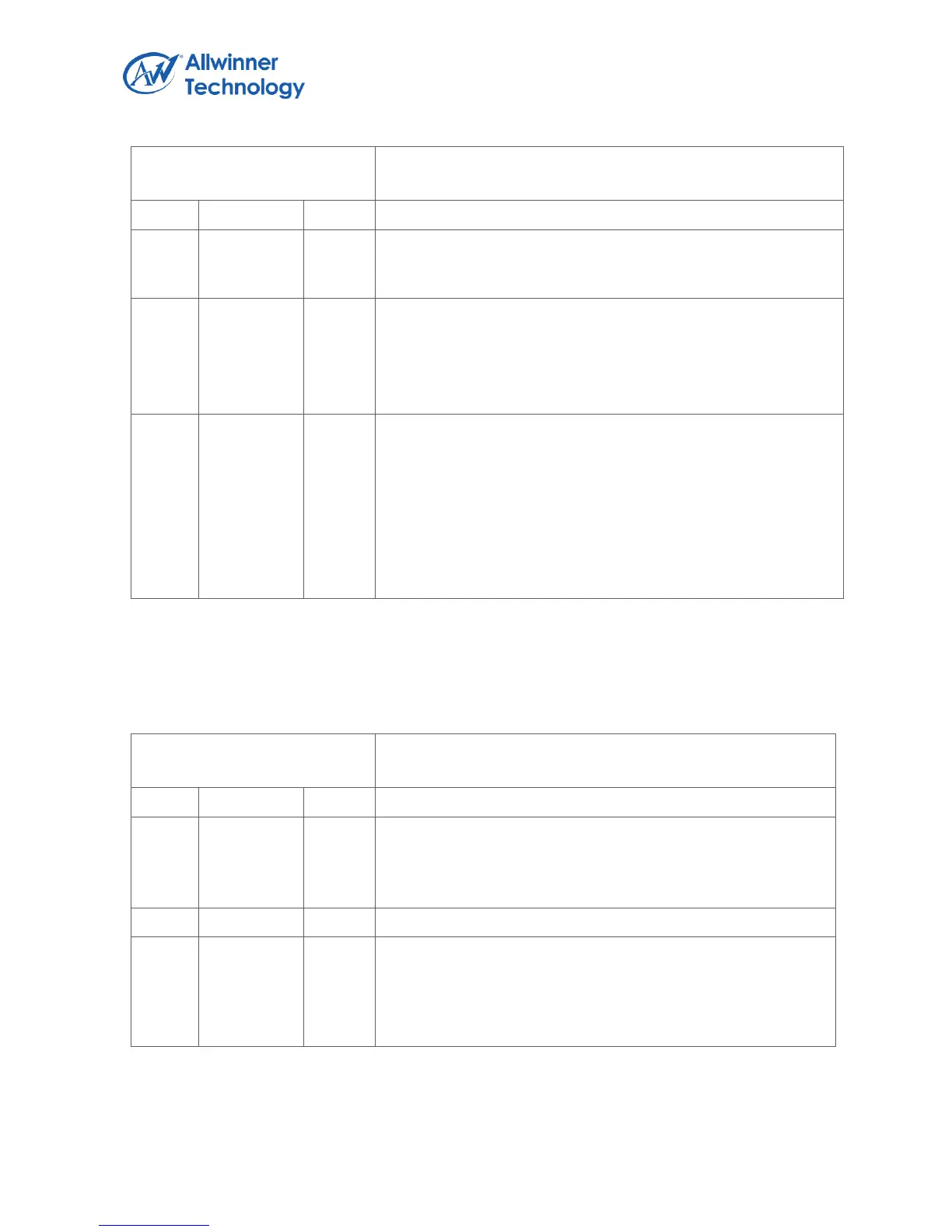

6.14.5.9. SMART CARD READER CHARACTER TIME REGISTER

Register Name: SCR_CTIM

Default Value: 0x00000000

CHARLIMIT

Character Limit. This 16-bit register sets the maximum time

between the leading edges of two consecutive characters. The

value is ETUs.

GUARDTIME

Character Guard time. This 8-bit register sets a delay at the

end of each character transmitted from the Smart Card Reader

to the Smart Card. The value is in ETUs. The parity error is

besides signaled during the guard time.

Loading...

Loading...