A20 User Manual (Revision 1.2) Copyright © 2013 Allwinner Technology Co., Ltd. All Rights Reserved. Page 90 / 812

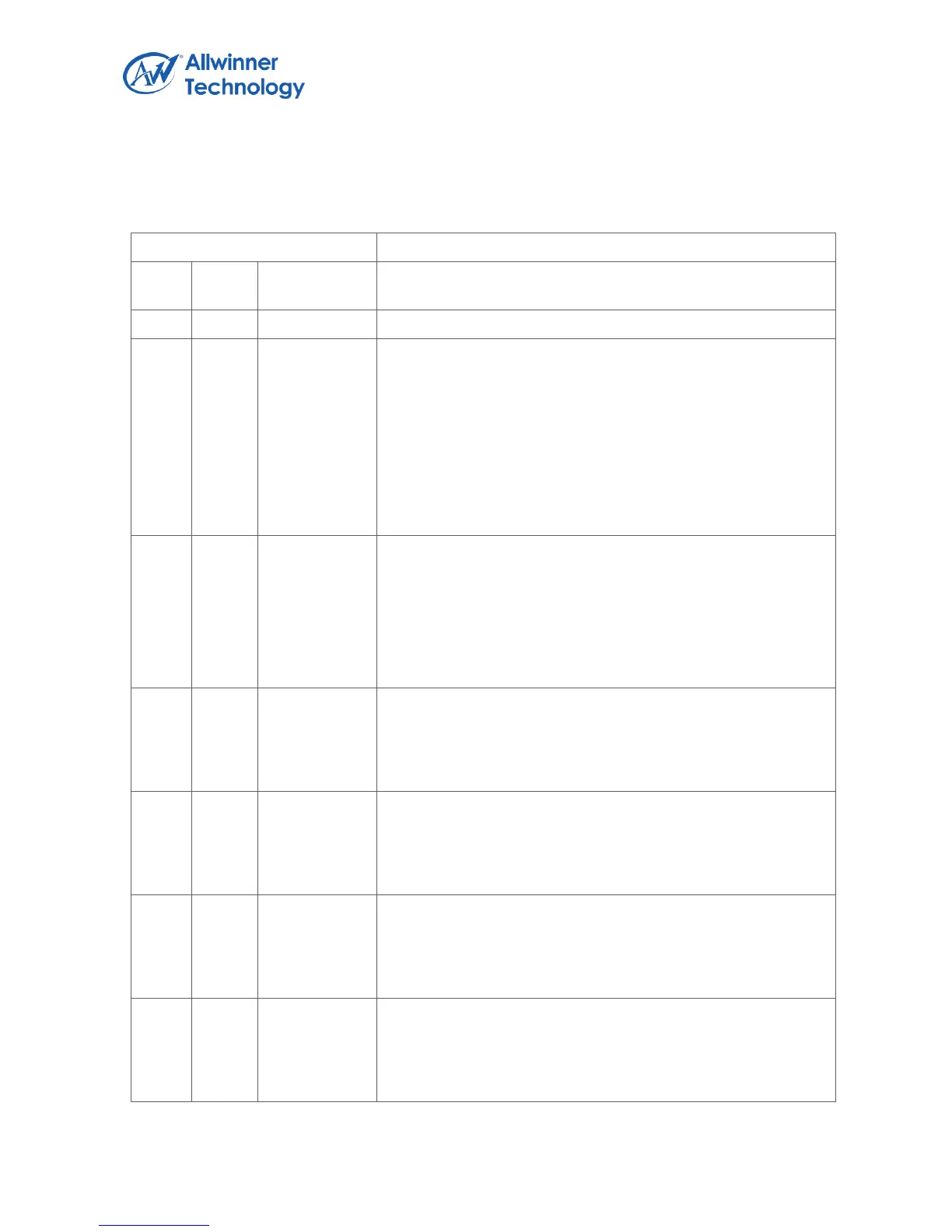

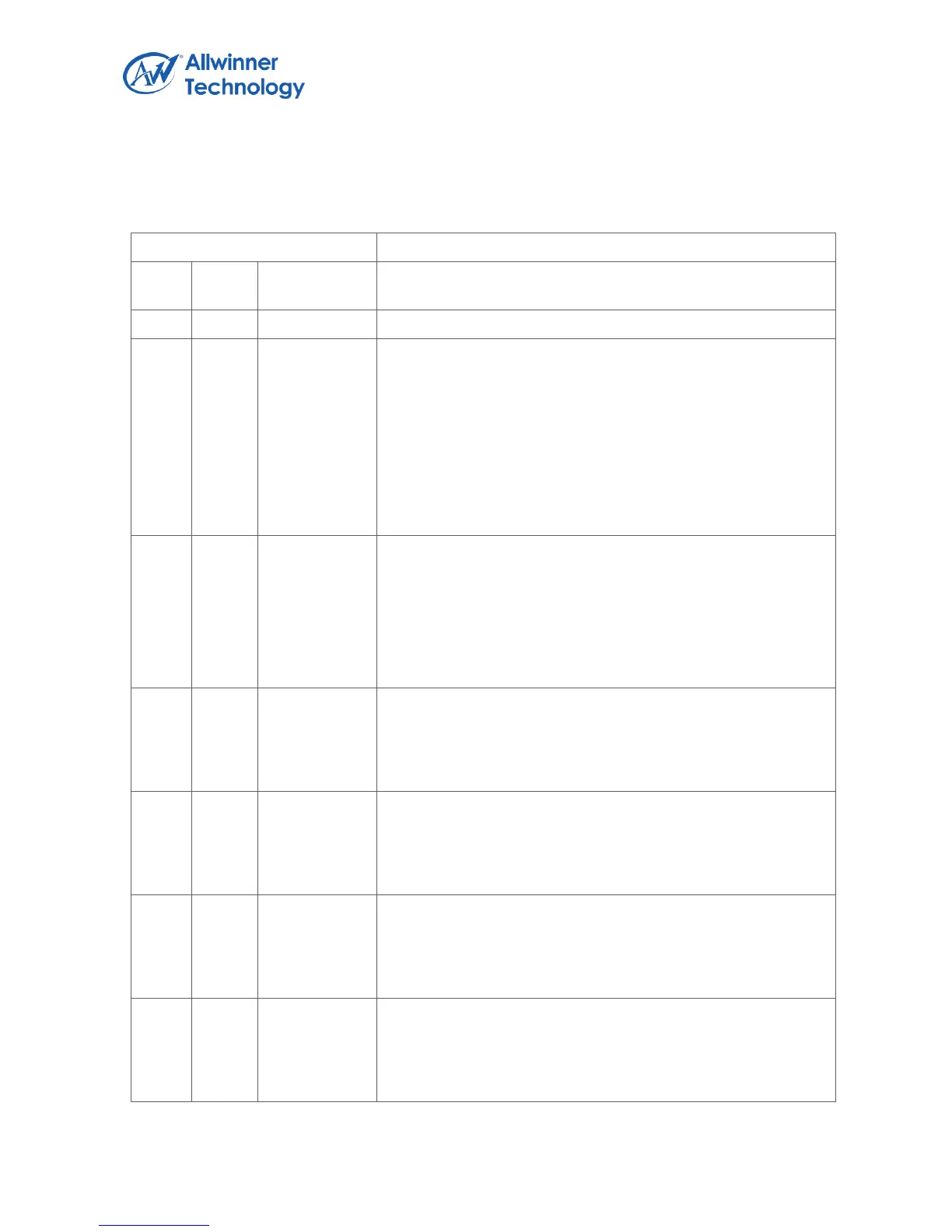

1.5.4.65. GMAC CLOCK REGISTER (DEFAULT: 0X00000000)

Register Name: GMAC_CLK_REG

TXC_DIV_CFG

Clock pre-divide ratio(n)

External transmit clock (125MHz) is pre-divided by as follows

for RGMII.

00:/1, generate 125MHz;

01:/5,generate 25 MHz;

10: /50,generate 2.5 MHz

11: Reserved

GRXDC

Configure GMAC Receive Clock Delay Chian.

000:

001:

…

111:

GRXIE

Enable GMAC Receive Clock Invertor.

0: Disable;

1: Enable;

GTXIE

Enable GMAC Transmit Clock Invertor.

0: Disable;

1: Enable;

GPIT

GMAC PHY Interface Type

0: MII;

1: RGMII;

GTCS

GMAC Transmit Clock Source

00: Transmit clock source for MII;

01: External transmit clock source(125MHz) for RGMII;

Loading...

Loading...