3 Device AGP MotherBoard Design

3-8

Intel740™ Graphics Accelerator Design Guide

3.1.5.3 Clock Issues

Supplying a clock to both AGP master devices raises issues that must be considered when

implementing a logical point-to-point bus. Among these issues are clock signal quality, routing,

and clock skew. Signal quality and routing are of a major concern since the clock now must be

routed to both master components.

A separate clock driver was used to drive the AGP clocks on this design. The topology for each

clock is point-to-point and no segment tuning between master devices is required. However, each

clock length must still be tuned to the target clock for clock skew reasons. Since separate clock

drivers are used, the skew between clock driver outputs must be taken into account in the overall

clock skew budget. The output to output skew for the clock chip was 0.25 ns.

Skew between each AGP master clock input and the AGP target (chipset) must be within the 1ns

limit called out in the AGP specification, Since we had a driver skew of 0.25ns due to the clock

drivers, this meant that our propagation delays and settling times skews could not exceed 0.75 ns.

This means that for a single clock driver solution not only must each of the two clock trace

segments be balanced in such a way that signal quality is acceptable, but the trace segments must

be tuned in such a way as to meet the AGP specified skew requirements.

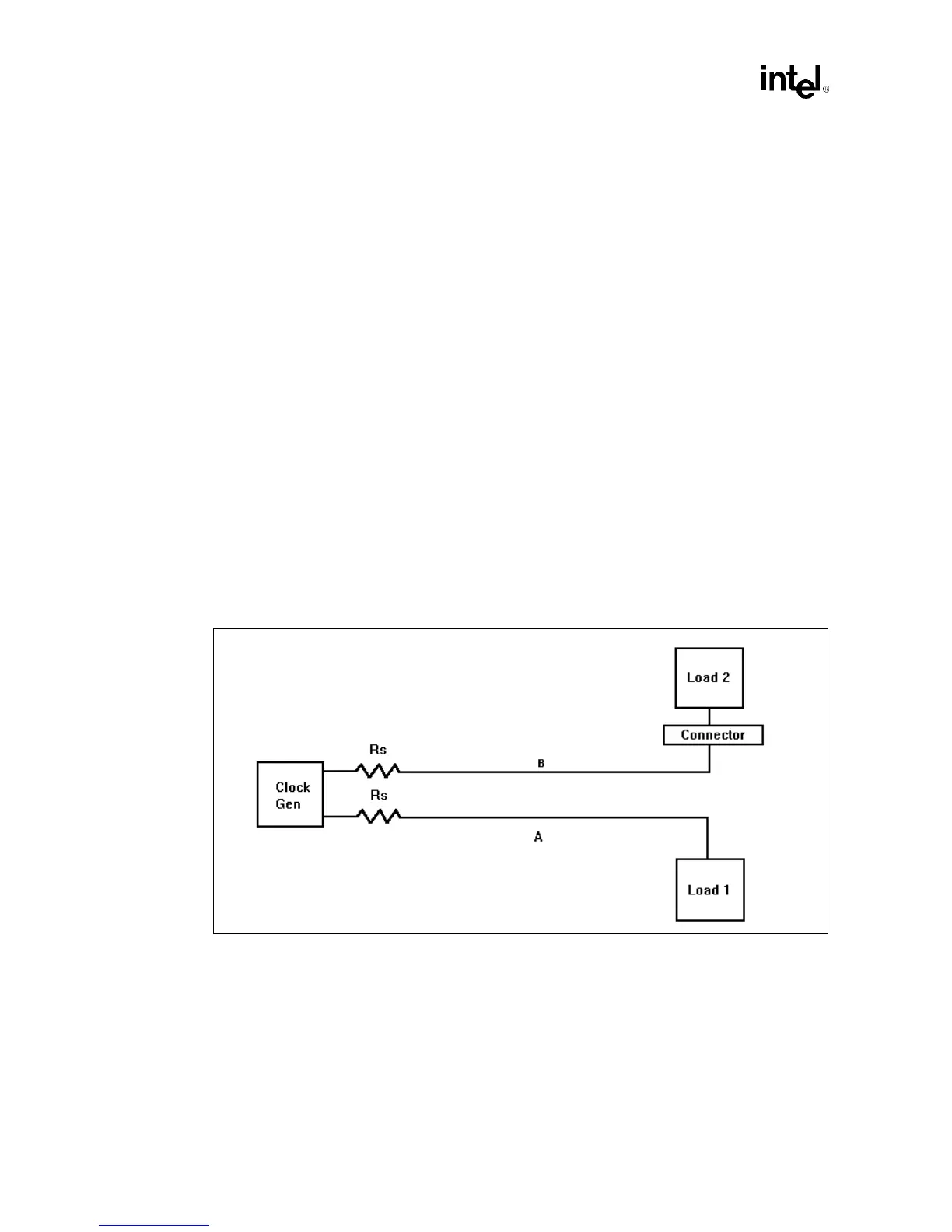

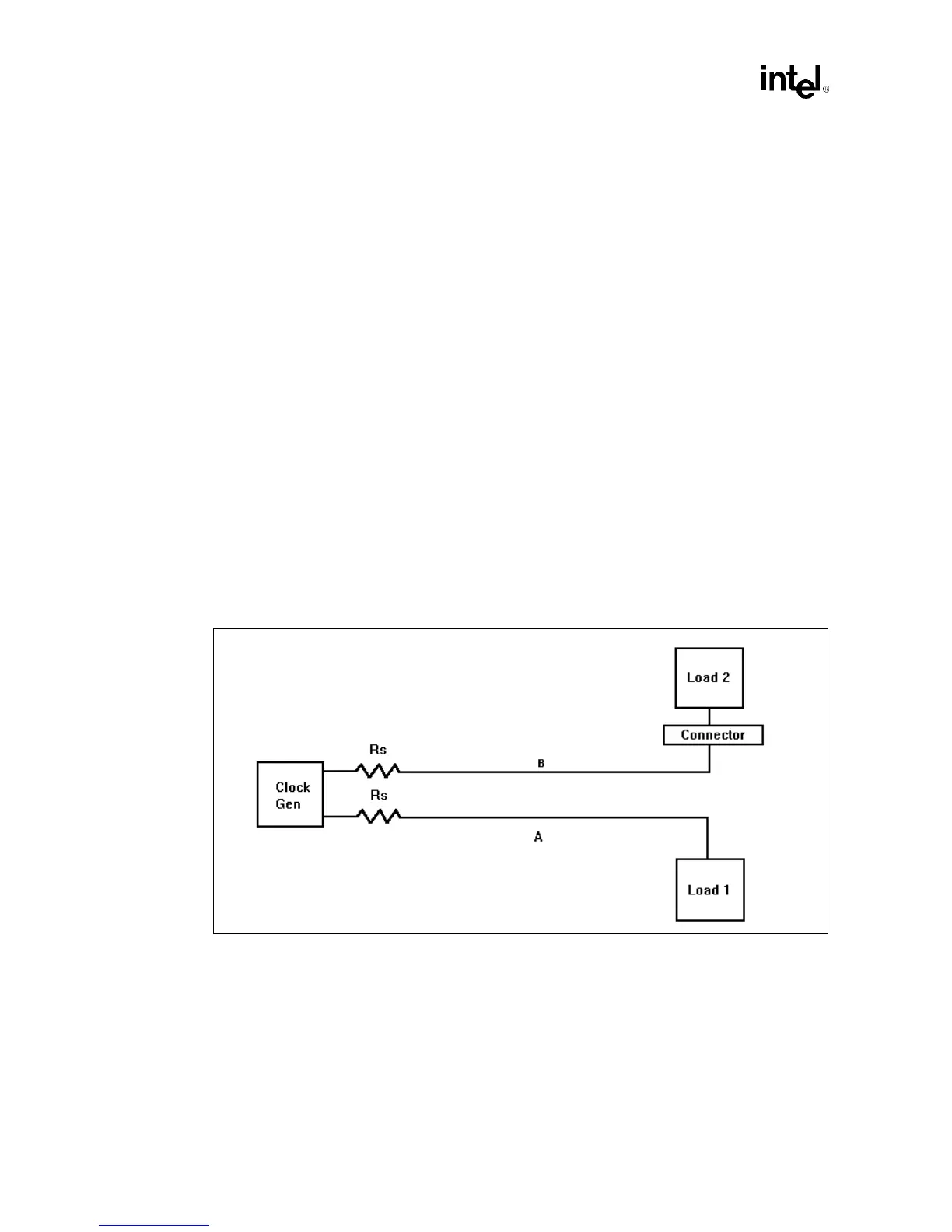

The clock topologies used are shown in Figure 3-6. This figure shows the clock topology if three

clock outputs are available. Each clock is a direct connection to it's respective load. Here the trace

segments A and B must be balanced with respect to the target device clock trace in such a way as to

meet system clock skew requirements. As mentioned previously, the clock generator output to

output skew must also be factored into the overall system clock skew budget. In this topology the

AGP target device is assumed to have a separate clock driver and is not shown here.

Figure 3-6. Point-to-Point Topology

Loading...

Loading...