Revision 0.91

19

SO-DIMM Module — Unbuffered SDRAM/SGRAM Graphics

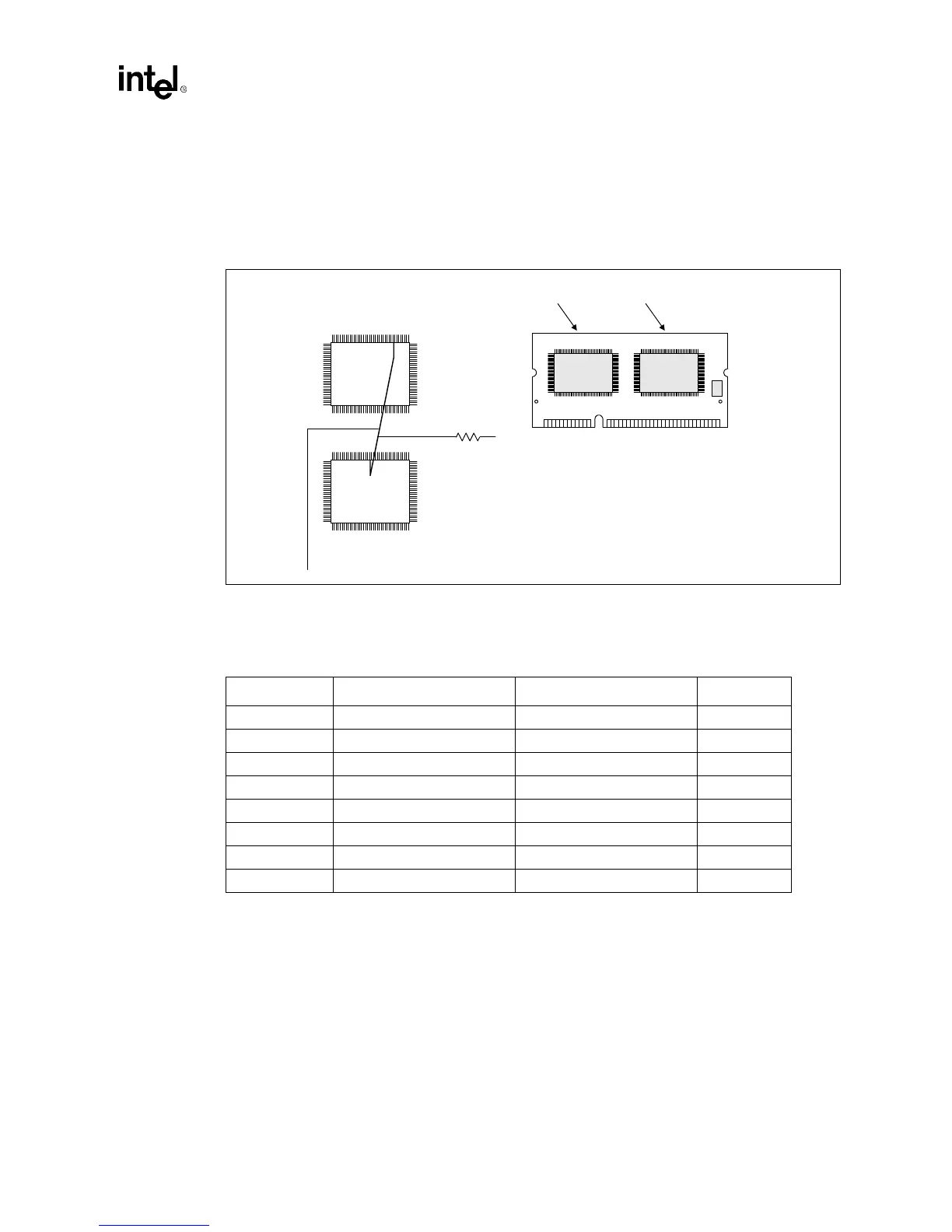

8.3 Data Routing

Data lodading is two loads per line, maximum. Routing should be performed using a T-topology, as

shown below.

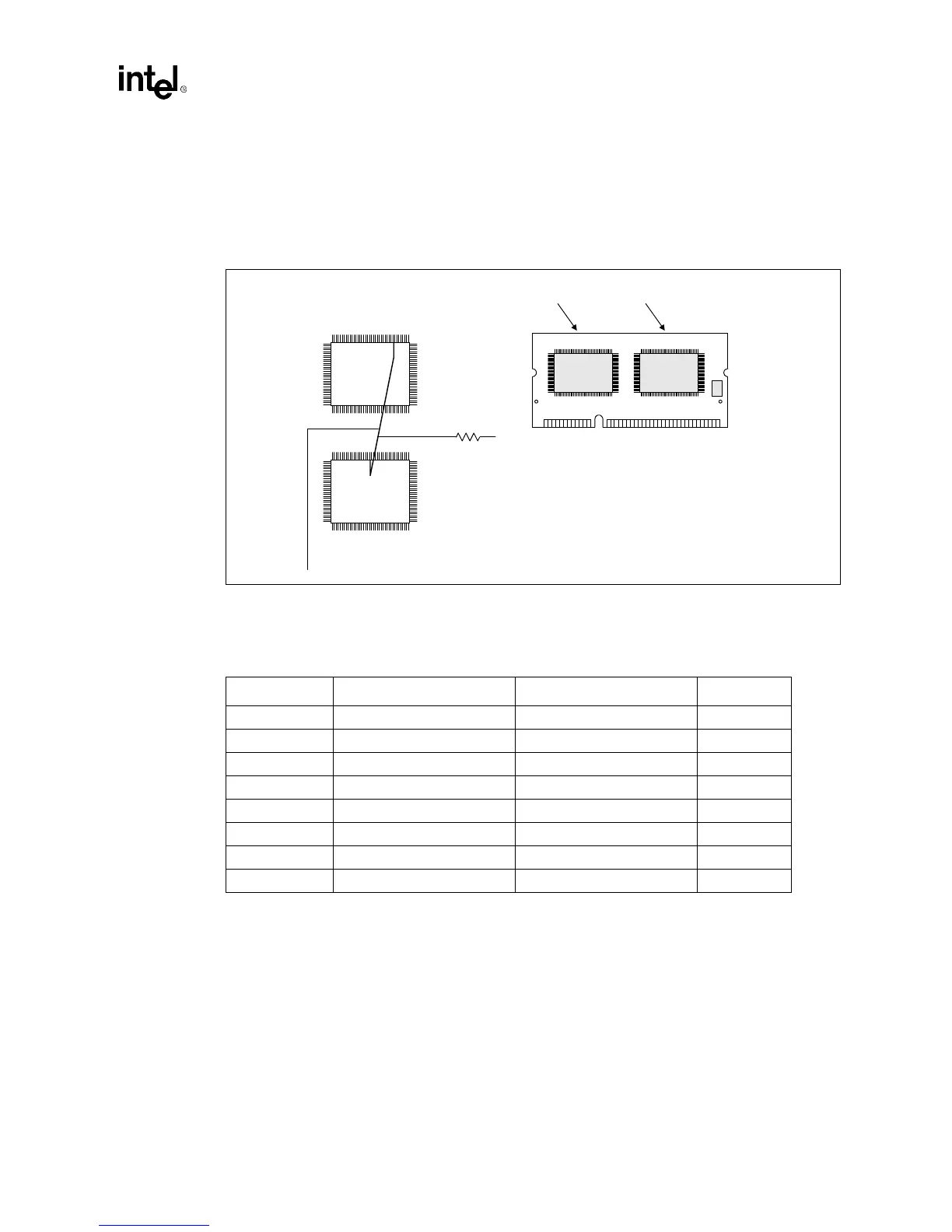

Byte-ordering (along with the respective Data Mask, DQM) within the SDRAM/SGRAM should

be swapped to optimize routing.

The following table lists the allowable stub lengths for the data line routing.

Figure 11.Data Routing

A010.vsd

a

o

Bank 0

d

c

A B

S

CD

b

o

Bank 1

Table 8. Byte Ordering

Module Byte Front-Side Memory Byte Back-Side Memory Byte

n

value

BYTE 0 Memory B; BYTE 0 Memory D; BYTE 3

n

= 115 pS

BYTE 1 Memory B; BYTE 3 Memory D; BYTE 0

n

= 35 pS

BYTE 2 Memory B; BYTE 1 Memory D; BYTE 2

n

= 35 pS

BYTE 3 Memory B; BYTE 2 Memory D; BYTE 1

n

= 115 pS

BYTE 4 Memory A; BYTE 1 Memory C; BYTE 2

n

= 115 pS

BYTE 5 Memory A; BYTE 2 Memory C; BYTE 1

n

= 35 pS

BYTE 6 Memory A; BYTE 0 Memory C; BYTE 3

n

= 35 pS

BYTE 7 Memory A; BYTE 3 Memory C; BYTE 0

n

= 115 pS

Loading...

Loading...