Intel740™ Graphics Accelerator Design Guide

3-13

3 Device AGP MotherBoard Design

results. The benefit to the former method is that a solution space can be determined before any

placement and routing is attempted. This saves time and effort over the method of route, simulate,

adjust.

It is, therefore, recommended that the simulation results for the 3-load bus drive the layout and

routing. The simulation results will produce a solution space for a particular set of buffer and board

conditions. This solution space will give the lengths and conditions for all segments of the 3-load

bus. It may be found that the given lengths and/or conditions governing the segments may not be

able to be routed for the placement needed on a given board. If this is the case, several options may

be pursued. The first is possible modifications to board placement of components. Placement may

be adjusted so that the solution space is now able to be routed.

If placement changes are not achievable, tradeoffs in the solution space may be tried. As will be

seen later in the Sensitivity Analysis section, changes in length requirements to a particular

segment of the topology will result in changes to other segments allowable length and constraints.

For example, the maximum allowed length of one segment may be to short to route but the

maximum allowed length of another segment may not be needed. By shortening one segment’s

maximum allowable length, additional length may be gained in another segment to enable routing

of the bus. In another case the solution space found may allow a particular routing mismatch

between data and strobe lines on the motherboard. By routing with no mismatch between data and

strobe lines on the motherboard, length may be gained in one or more segments.

Another option to change the solution space can be to change the board parameters. These

parameters include trace width and space, impedance and variation, and/or dielectric thickness. All

of these parameters may have an effect on the solution space which could allow the bus to be

routed. Note that is has been shown that moving to a wider trace and space ratio has increased the

segment length for the 3-load bus. The length gained to enable routing the bus comes at the cost of

increased routing area required by the increased trace and space ratios.

Flight time and skew constraints as well as electrical characteristics set forth in the AGP

specification must be followed when designing a logical point-to-point bus. The trace lengths, and

allowable trace routing skew lengths may be different than in the case of a physical point-to-point

bus, but the actual time allotted for flight time and signal skew must be the same in both cases.

It should be noted that not all implementations of a logical point-to-point bus will yield the same

routing solution space. Issues that effect the trace length and routing mismatch allowed in a

particular implementation include board impedance range, impedance variations due to crosstalk,

and buffer characteristics for both the target (chipset) and master graphics controller down on the

motherboard. Variations in all of these areas will yield different simulation results and thus

different routing solution spaces. Because of this potential difference in each individual solution,

each implementation of a point-to-point bus should be carefully simulated.

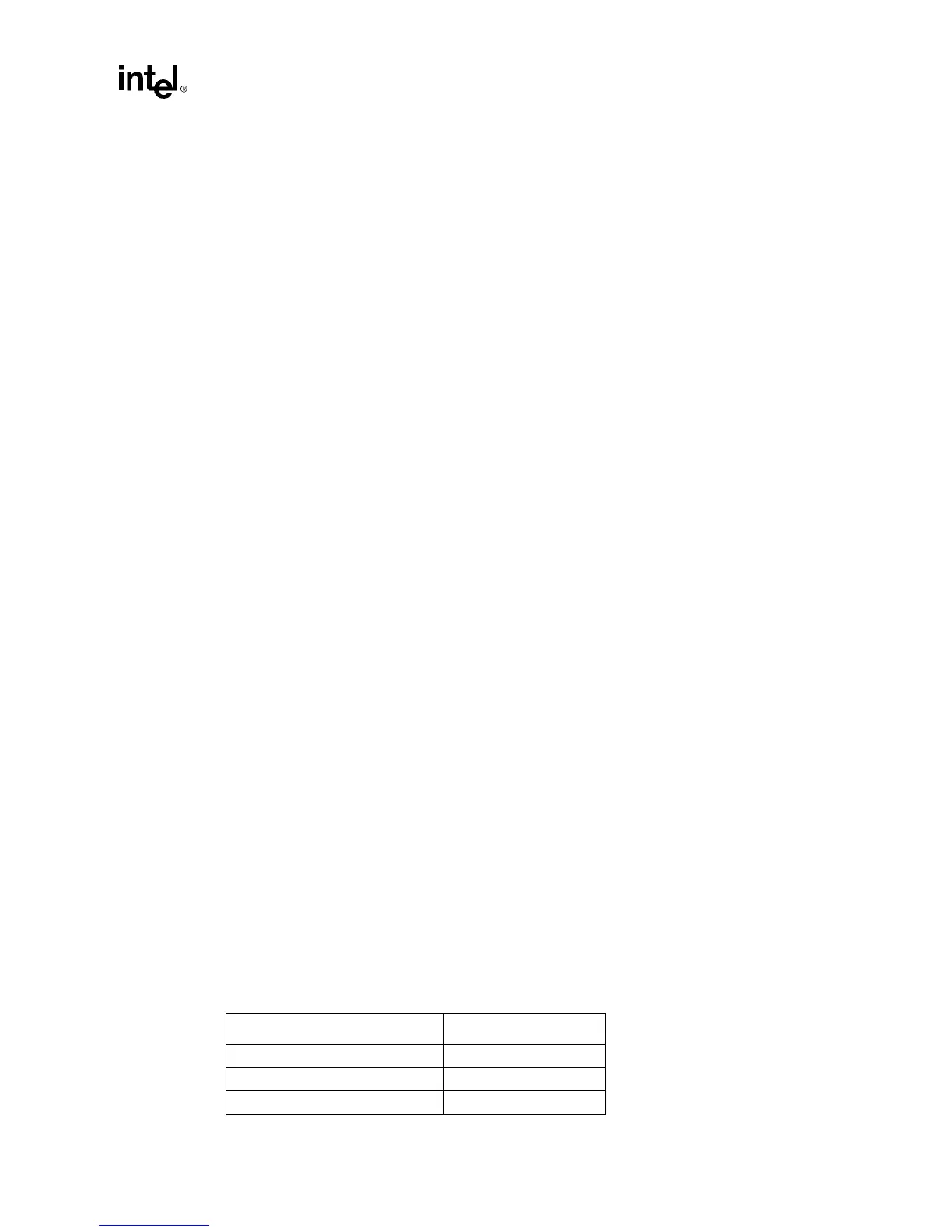

3.2.3.2 Data and strobe definitions

Throughout this document, the term “data” refers to AD[31:0], C/BE[3:0]# and SAB[7:0]. The

term “strobe” refers to AD_STB[1:0] and SB_STB. When the term data is used it is referring to

one of three groups of data as seen in Table 3-3. When the term strobe is used it is referring to one

of the three strobes as it relates to the data in its associated group.

Table 3-3. Data and Associated Strobe

Data Associated Strobe

AD[15:0] and C/BE[1:0]# AD_STB0

AD[31:16] and C/BE[3:2]# AD_STB1

SBA[7:0] SB_STB

Loading...

Loading...