J-Link / J-Trace (UM08001) © 2004-2017 SEGGER Microcontroller GmbH & Co. KG

49

1.6 Built-in intelligence for supported CPU-cores

In general, there are two ways to support a CPU-core in the J-Link software:

1. Intelligence in the J-Link firmware

2. Intelligence on the PC-side (DLL)

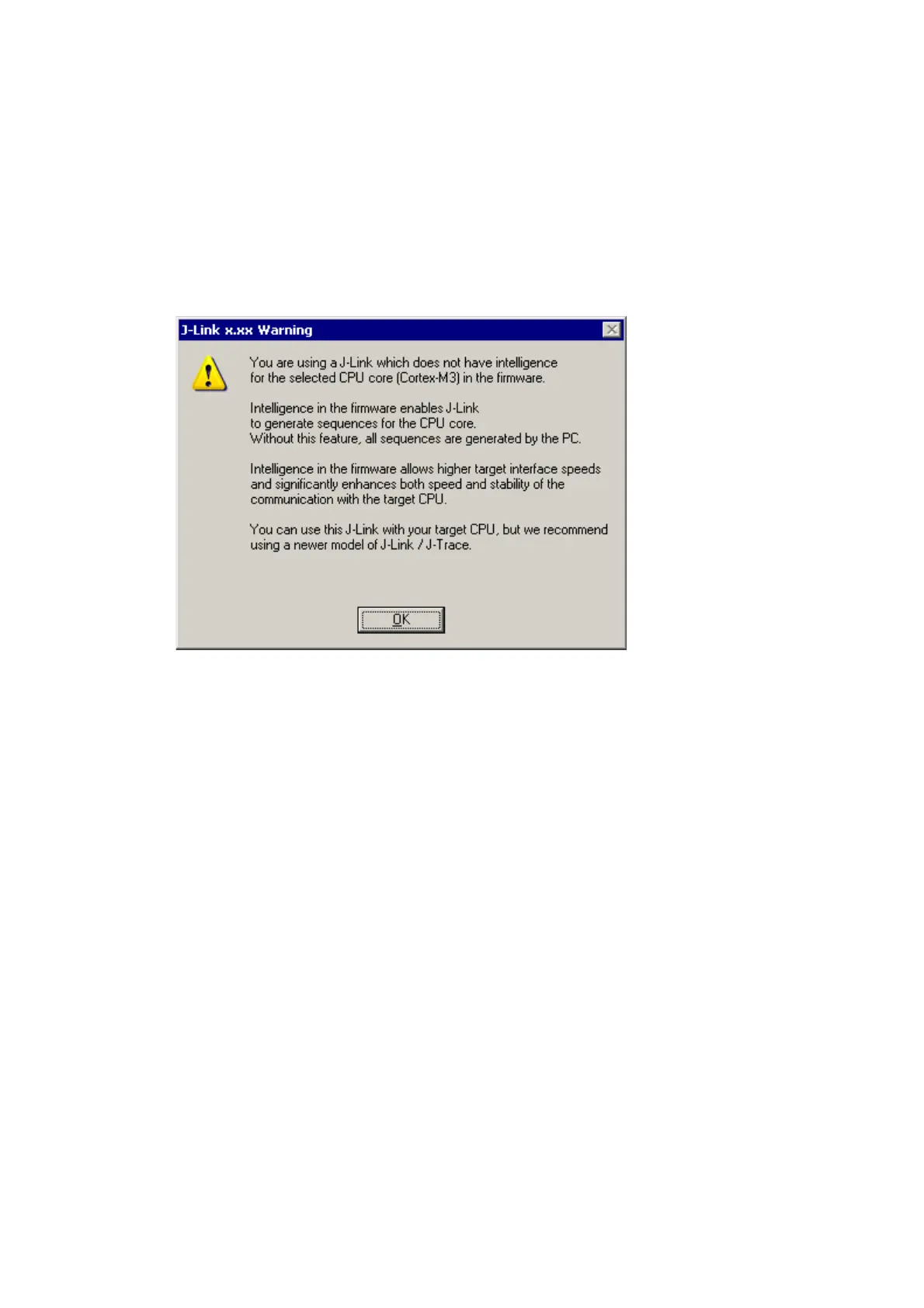

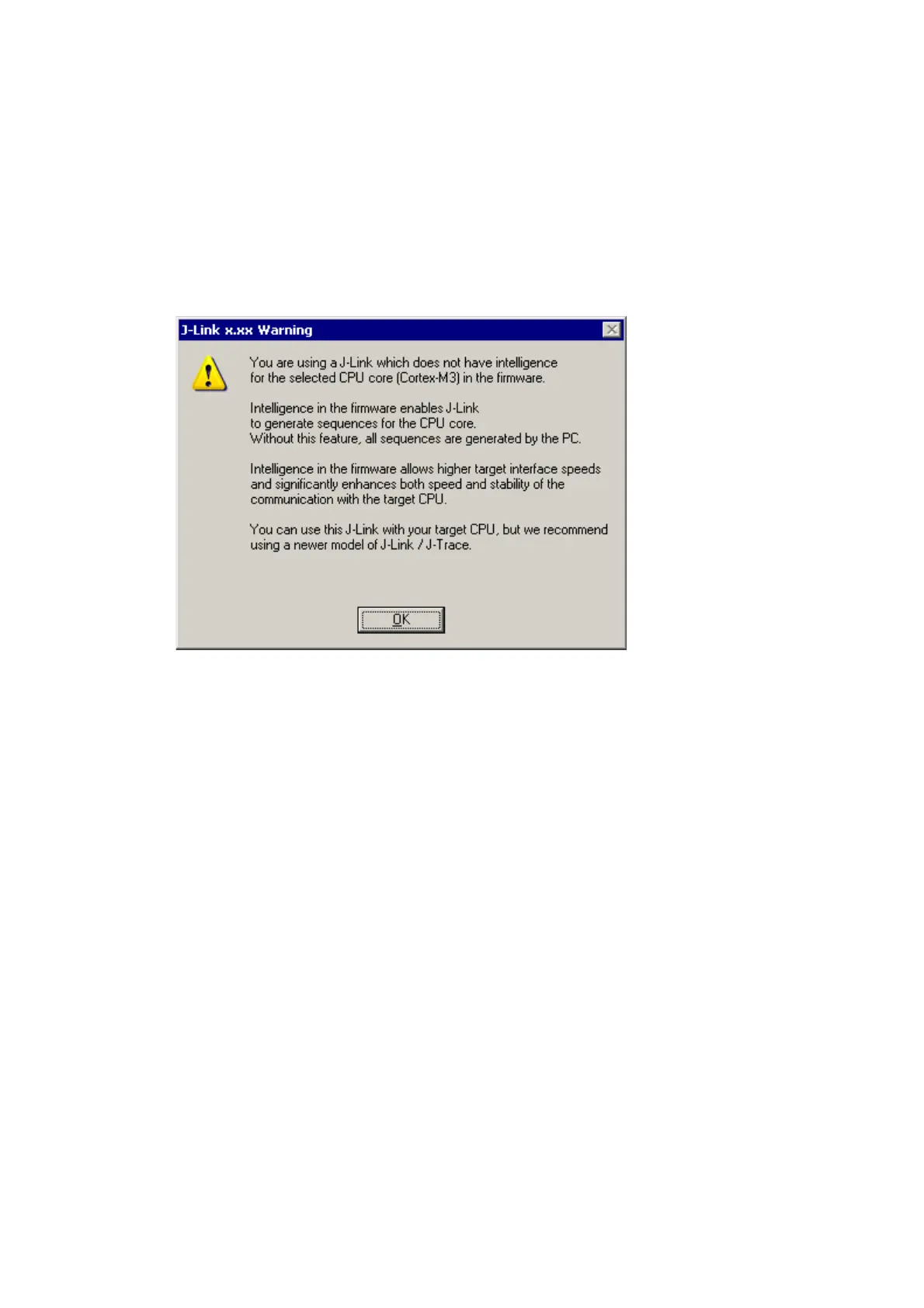

Having the intelligence in the firmware is ideal since it is much more powerful and

robust. The J-Link PC software automatically detects which implementation level is

supported for the connected CPU-core. If intelligence in the firmware is available, it

is used. If you are using a J-Link that does not have intelligence in the firmware and

only PC-side intelligence is available for the connected CPU, a warning message is

shown.

1.6.1 Intelligence in the J-Link firmware

On newer J-Links, the intelligence for a new CPU-core is also available in the J-Link

firmware which means that for these J-Links, the target sequences are no longer

generated on the PC-side but directly inside the J-Link. Having the intelligence in the

firmware leads to improved stability and higher performance.

1.6.2 Intelligence on the PC-side (DLL)

This is the basic implementation level for support of a CPU-core. This implementation

is not J-Link model dependent, since no intelligence for the CPU-core is necessary in

the J-Link firmware. This means, all target sequences (JTAG/SWD/...) are generated

on the PC-side and the J-Link simply sends out these sequences and sends the result

back to the DLL. Using this way of implementation also allows old J-Links to be used

with new CPU cores as long as a DLL-Version is used which has intelligence for the

CPU.

But there is one big disadvantage of implementing the CPU core support on the DLL-

side: For every sequence which shall be sent to the target a USB or Ethernet transac-

tion is triggered. The long latency especially on a USB connection significantly affects

the performance of J-Link. This is true especially when performing actions where J-

Link has to wait for the CPU frequently. An example is a memory read/write operation

which needs to be followed by status read operations or repeated until the memory

operation is completed. Performing this kind of task with only PC-side intelligence

requires to either make some assumption like: Operation is completed after a given

number of cycles. Or it requires to make a lot of USB/Ethernet transactions. The first

option (fast mode) will not work under some circumstances such as low CPU speeds,

the second (slow mode) will be more reliable but very slow due to the high number of

USB/Ethernet transactions. It simply boils down to: The best solution is having intel-

ligence in the emulator itself!

Loading...

Loading...