Debug support (DBG) RM0090

1680/1731 DocID018909 Rev 11

38.8 SW debug port

38.8.1 SW protocol introduction

This synchronous serial protocol uses two pins:

• SWCLK: clock from host to target

• SWDIO: bidirectional

The protocol allows two banks of registers (DPACC registers and APACC registers) to be

read and written to.

Bits are transferred LSB-first on the wire.

For SWDIO bidirectional management, the line must be pulled-up on the board (100 KΩ

recommended by ARM

®

).

Each time the direction of SWDIO changes in the protocol, a turnaround time is inserted

where the line is not driven by the host nor the target. By default, this turnaround time is one

bit time, however this can be adjusted by configuring the SWCLK frequency.

38.8.2 SW protocol sequence

Each sequence consist of three phases:

1. Packet request (8 bits) transmitted by the host

2. Acknowledge response (3 bits) transmitted by the target

3. Data transfer phase (33 bits) transmitted by the host or the target

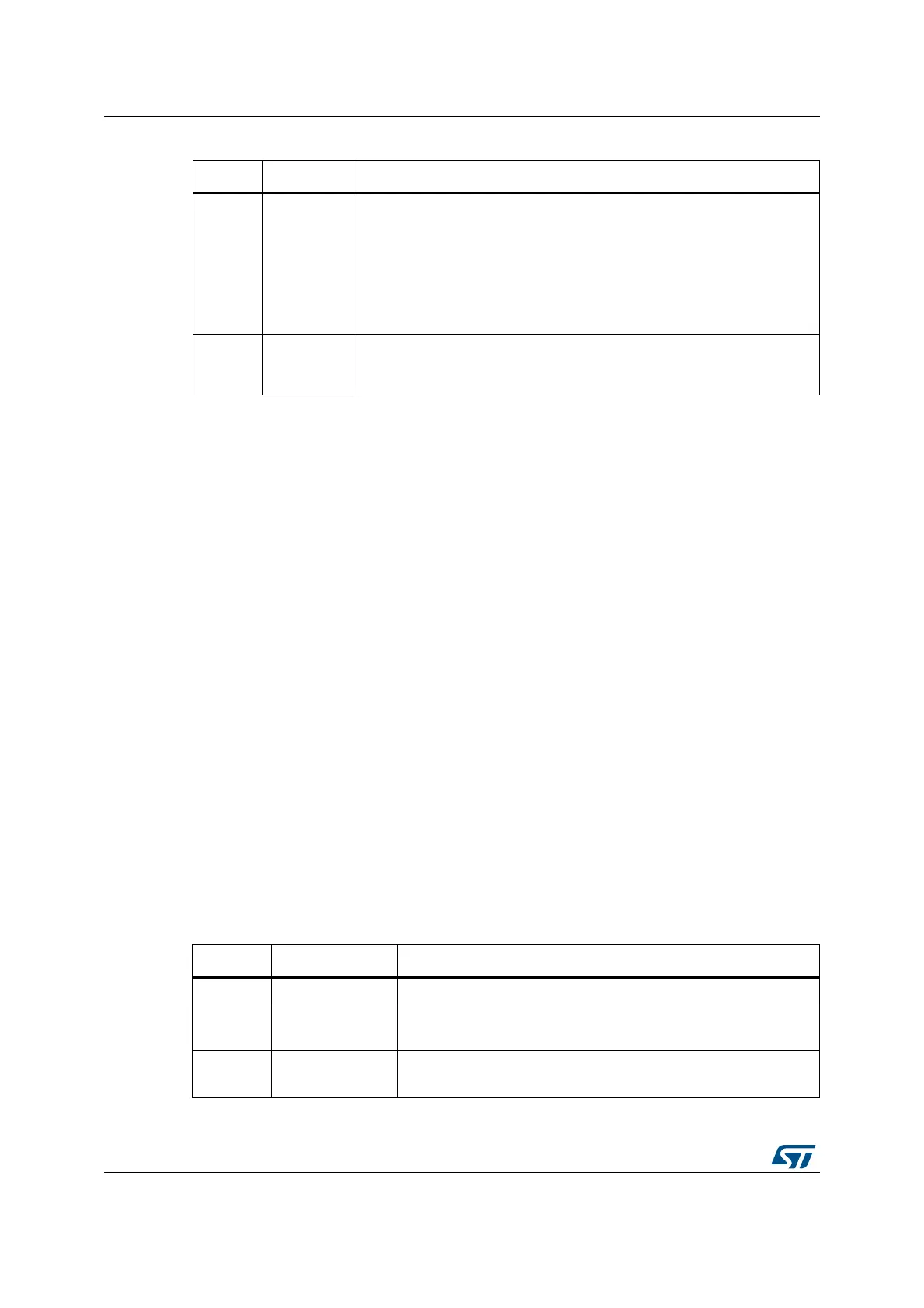

0x8 10

DP SELECT register: Used to select the current access port and the

active 4-words register window.

– Bits 31:24: APSEL: select the current AP

– Bits 23:8: reserved

– Bits 7:4: APBANKSEL: select the active 4-words register window on the

current AP

– Bits 3:0: reserved

0xC 11

DP RDBUFF register: Used to allow the debugger to get the final result

after a sequence of operations (without requesting new JTAG-DP

operation)

Table 296. 32-bit debug port registers addressed through the shifted value A[3:2]

Address A[3:2] value Description

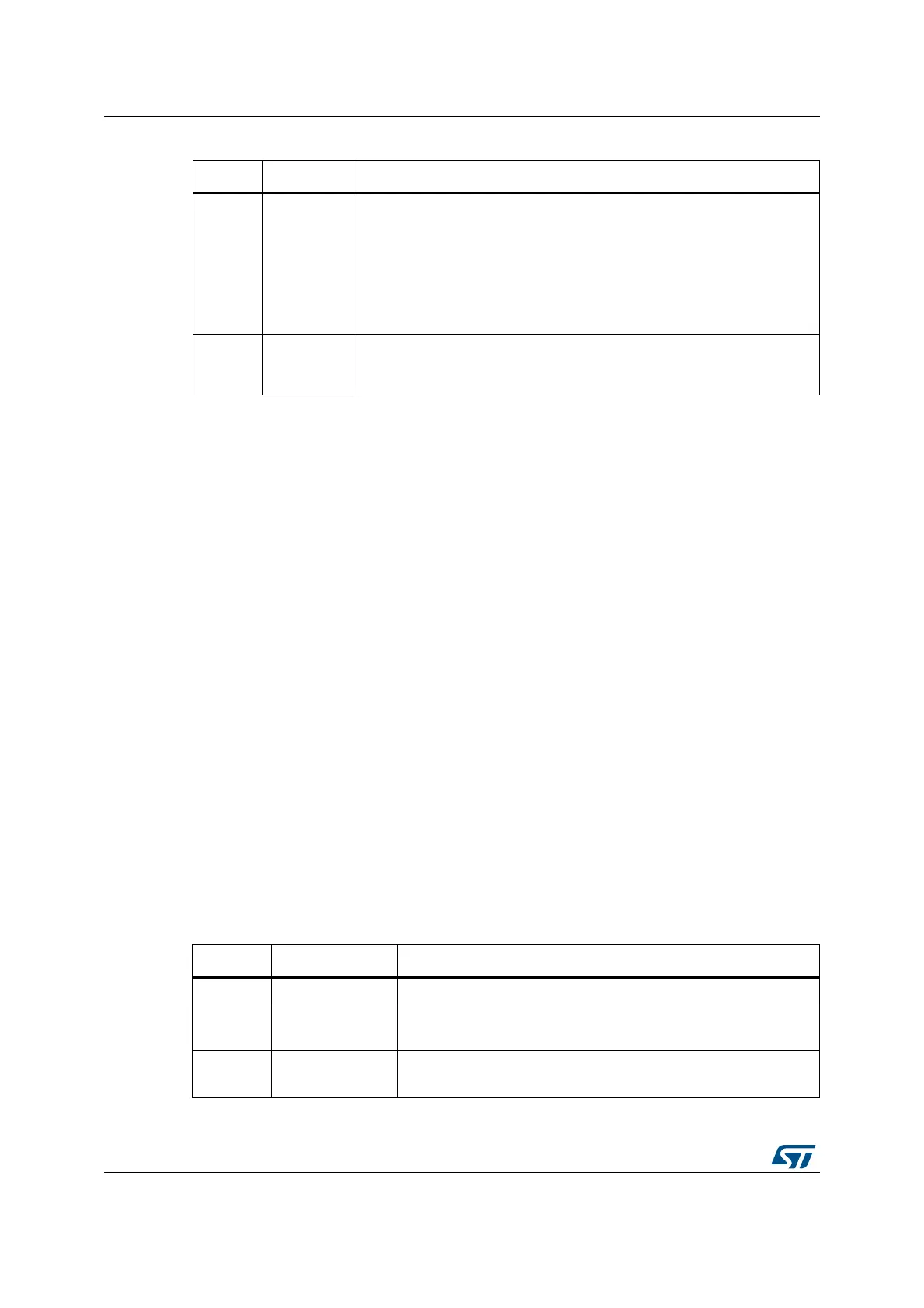

Table 297. Packet request (8-bits)

Bit Name Description

0 Start Must be “1”

1 APnDP

0: DP Access

1: AP Access

2RnW

0: Write Request

1: Read Request

Loading...

Loading...